© 2005 - 2009 JATIT. All rights reserved.

www.jatit.org

# CONTROL OF THREE LEVEL INVERTER BASED DYNAMIC VOLTAGE RESTORER

## <sup>1</sup>S.LEELA, <sup>2</sup>S.S.DASH

<sup>1</sup> Research Scholar, Dept.of Electrical & Electronics Engg., Bharath University, Chennai, India-600073.

<sup>2</sup> Prof., Department of Electrical & Electronics Engineering, SRM University, Chennai, India -603203.

E-mail: <a href="mailto:sleela13@yahoo.in">sleela13@yahoo.in</a>, <a href="mailto:munu\_dash\_2K@yahoo.com">munu\_dash\_2K@yahoo.com</a>

#### ABSTRACT

This paper deals with modelling and digital simulation of three level inverter based Dynamic Voltage Restorer(DVR). The control of DVR that injects a voltage in series with a distribution feeder is presented. DVR is a power electronic controller that can protect sensitive loads from disturbances in supply system. It is observed that DVR can regulate the voltage at the load. Circuit model is developed and the same is used for simulation studies.

Keywords: Dynamic Voltage Restorer(DVR), Matlab simulink, Series Compensation, 3 level inverter

#### **1. INTRODUCTION**

A power electronic converter based series compensator that can protect critical loads from all supply side disturbances other than outages is called a dynamic voltage restorer. The restorer is capable of generating or absorbing independently controllable real and reactive power at its AC output terminal. This device employs solid state power electronic switches in a pulse width modulated (PWM) inverter structure. It injects a set of three phase AC output voltages in series and synchronism with the distribution feeder voltages. The amplitude and phase angle of the injected voltages are variable there by allowing control of the real and reactive power exchange between the device and the distribution system. The DC input terminal of the restorer is connected to an energy source or an energy storage device of appropriate capacity. The reactive power exchanged between the restorer and the distribution system is internally generated by the restorer without AC passive reactive components. The real power exchanged at the restorer output AC terminals is provided by the restorer input DC terminal from an external energy source or energy storage system. In August 1996, Westinghouse Electric Corporation installed world's first dynamic voltage restorer in Duke Power Company's 12.47 kV substation in Anderson, South Carolina, This was installed to provide protection to an automated rug manufacturing plant. Prior to this connection, the

restorer was first installed at the Waltz Mill test facility near Pittsburgh for the full power tests. The test results are discussed in [1]. The next commissioning of the restorer was done at Westinghouse in February 1997 in Powercor's 22 kV distribution system at Stanhope, Victoria, Australia to protect a diary milk processing plant. The saving that results from the installation of this installation is estimated at over \$100,000 per year [2]. In the next phase of development, Westinghouse (now taken over by Siemens) installed world's first platform mounted dynamic voltage restorer to protect Northern Lights Community College and several other smaller loads in Dawson Creek, British Columbia, Canada [3].

This paper extends the concept of dynamic voltage restorer further to tightly regulate the load voltage. It can also perform the primary functions of the restorer, i.e., to protect the load from temporary voltage interruption, sag/swell etc. This device is called a dynamic voltage regulator (DVR). For the control operation of DVR we stipulate that real power supplied by the device in steady state is zero. Based on this stipulation, the references of the voltages that are to be injected in series are generated. This requires online extraction of the fundamental positive sequence based on the sampled values. Once the reference voltage s are obtained, they are tracked by the VSIs realizing the DVR.

www.jatit.org

The actual implementation of the DVR using inverters raises additional issues of switch frequency injection. To eliminate these, two different filter structures are discussed here. The inclusion of the filters further complicates the problem of voltage tracking. To facilitate proper voltage tracking a switching band control scheme is used here. The proposed DVR is validated through digital computer simulation studies. New approach to load balancing and power factor correction is given by Ghosh[4]. Power inverter operations for series compensation is given by [5]. Transient analysis of alternator is given by [6].

The above literature does not deal with the modelling of DVR system using matlab simulink. In this work, an attempt is made to model and simulate the DVR system using simulink.

#### 2. DVR CHARACTERISTICS

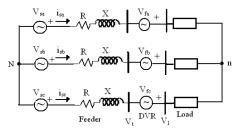

In this section we shall present the fundamental, positive-sequence, steady state analysis of a DVR connected power system. The voltage regulation scheme is shown in Figure.1. This consists the following:

- DVR: represented by voltage sources  $V_{fa}$ ,  $V_{fb}$  and  $V_{fc}$

- Supply voltage: represented by sources V<sub>sa</sub>, V<sub>sb</sub> and V<sub>sc</sub>

The DVR is connected between a terminal bus on the left and a load bus on the right. The voltage sources are connected to the DVR terminals by a feeder with an impedance of R+jX. We shall assume that the loads are balanced and the load impedance is given by  $Z_I = R_I + jX_I$ . It is to be noted that the phase angle  $\Phi_I$  between the load terminal V<sub>1</sub> and the line current is depends on the load impedance and is independent of the line impedance or the DVR voltage.

Figure.1. Schematic diagram of a DVR connected to a power system.

The objective of the discussion presented below is to regulate the magnitude of the load voltage

equal to that of the source voltage through DVR voltage injection. Further we stipulate the following condition on the DVR:

• The DVR does not supply any real power in the steady state. This implies that the phase angle difference between DVR voltage phasor and line current phasor must be  $\Pi$  /2 in the steady state.

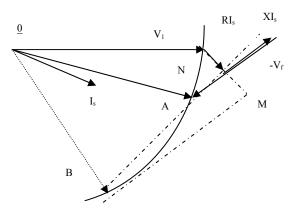

Let us assume that the load current lags the load voltage. To draw a phasor diagram of the steady state operation, we assume that the load voltage is fixed at V per unit and the source voltage is allowed to vary. Since the primary target is to make the magnitudes of  $V_1$  and Vs equal, the locus of desirable  $V_s$  is the arc NB as shown in Figure.2.

To make the magnitude of the load voltage equal to that of the source voltage, the RI<sub>s</sub> drop must be less than NM. If the drop is less than this limiting value, the DVR must compensate the entire reactive drop in the feeder and provide additional injection such that the source voltage becomes V per unit.

Figure.2. Phasor diagram showing multiple solutions

It can be seen from Figure.2 that there are two possible intersection points with the arcone at A and the other at B. This implies that two possible values of DVR voltage and can be obtained for each feeder drop. For the first value, the source voltage will be along OA, while for the other value, it will along OB. It is needless to say that the best choice is the A intersection requiring much smaller voltage injection from the DVR.

Example 1: In this example, we illustrate the procedure for the steady-state computation of

© 2005 - 2009 JATIT. All rights reserved.

www.jatit.org

DVR voltage. Let the feeder impedance be 0.5+j0.3 per unit, while the load impedance be 2.5+j2 per unit. We now connect a DVR aiming to regulate the load voltage to 1.0 per unit. Let us assume that rms load voltage is given by  $\vec{V_l} = 1 \ge 0^0$  per unit. The line current is then

$$I_s = \frac{1 \angle 0^0}{R_l + jX_l} = 0.3123 \angle -38.66^0$$

p.u

For zero DVR power, its voltage must be in quadrature to the line current. We then have

$$\vec{V}_{f} = \left| \vec{V}_{f} \right| e^{j \angle (\vec{l}_{s} + 90)} = \left| \vec{V}_{f} \right| \angle 51.34^{0} = \left| \vec{V}_{f} \right| (a_{1} + jb_{1})$$

$$\longrightarrow (1)$$

where  $a_1+jb_1$  is a unit phasor at 90° to  $I_s$ .

Again from Fig.1 we get

$$\vec{V}_s + \vec{V}_f = \vec{V}_l + (R + jX)\vec{I}_s = \vec{V}_l + a_2 + jb_2$$

(2)

where  $a_2 + jb_2$  represents the feeder drop. Substituting (1) in (2) and rearranging we get  $\vec{V_s} = \vec{V_l} + a_2 + jb_2 - |\vec{V_f}|(a_1 + jb_1)$

(3) The following quadratic equation is then obtained from the magnitude condition of (3)

$$\begin{aligned} \left| \vec{V}_{f} \right|^{2} &- 2 \left| a_{1} \left( \left| \vec{V}_{1} \right| + a_{2} \right) + b_{1} b_{2} \right) \left| \vec{V}_{f} \right| \\ &+ \left( \left| \vec{V}_{i} \right| + a_{2} \right)^{2} + b_{2}^{2} - \left| \vec{V}_{s} \right|^{2} = 0 \end{aligned}$$

$$(4)$$

Let us assume that the magnitude of the source voltage is 1.0 per unit. Then solving the above equation we get

$|\vec{V}_f| = 0.1137 \& 1.3231$

These two values of the magnitude of the injected voltage correspond to two operating points (A and B) in Figure 2. We shall obviously choose the lower of the two values.

#### 3. SIMULATION RESULTS

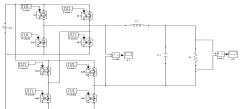

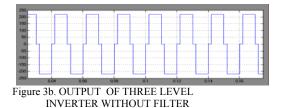

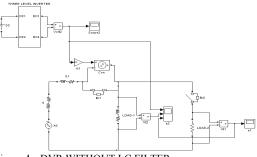

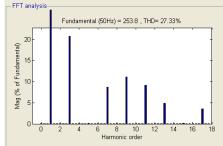

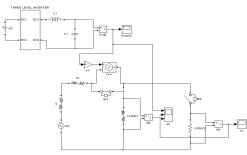

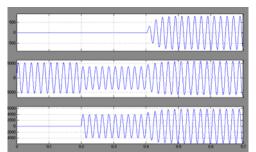

Digital simulation is done using the blocks of Matlab simulink and the results are presented here. Three level inverter system is shown in Figure 3a. The output of the inverter without filter is shown in Figure 3b. The output with filter is shown in Figure 3c. DVR using multilevel inverter is shown in Figure 4a. The output of the inverter is injected into line through a transformer. At t=0.2sec, the additional load is switched on. The voltage across load 1 decreases as shown in Figure 4b. DVR injects the voltage at t=0.4secs. The voltage across the loads 1 & 2 will resume to the normal value. FFT analysis for the output voltage is shown in Figure 4c. THD is 27.3%.

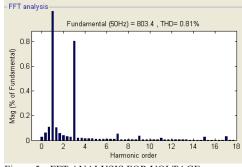

DVR system with LC filter is shown in Figure 5a. Injected voltage and the voltage across loads 1 & 2 are shown in Figure 5b. FFT analysis for the output voltage is shown in Figure 5c. THD reduces to 0.8%. Thus the harmonics are reduced from 27.3% to 0.8%.

Figure 3a. THREE LEVEL INVERTER

INVERTER WITH FILTER

Figure 4a. DVR WITHOUT LC FILTER

www.jatit.org

LOAD-1 &LOAD-2

Figure 4c. FFT ANALYSIS FOR VOLTAGE

Figure 5a. DVR WITH LC FILTER

Figure 5b. VOLTAGE ACROSS EXTERNAL, LOAD-1 &LOAD-2 WAVEFORMS

Figure 5c. FFT ANALYSIS FOR VOLTAGE

### 4. CONCLUSION

This paper presents circuit modelling and simulation of DVR using cascaded three level inverter. The pulses given to the inverter-II are shifted by  $36^{\circ}$  with respect to the pulses given to the inverter-I to reduce the harmonics. This paper demonstrates the capability of DVR to improve the voltage quality. Two different DVR structures are studied and the corresponding results are presented. It is better to use a filter in the output of inverter to reduce heating.

The simulation is based on the assumption of balanced load and single phase circuit model is considered. The simulation results are in line with the predictions.

## 5. REFERENCES:

- N.H.Woodley, L.Morgan and A.Sundaram, "Experience with an inverter-base d ynamic voltage restorer," *IEEE Trans. Power Delivery*, Vol. 14, No.3, pp.1181-1185, 1999.

- [2] N.H.Woodley,A.Sundaram,B.

CoulterandD.Morris, "Dynamic voltage restorer demonstration project experience," 12<sup>th</sup> Conf. Electric Power Supply Industry(CEPSI), Pattaya, Thailand, 1998.

- [3] N.H.Woodley, K.S. Berton, C.W.Edwards, B.Coulter, B.Ward, T.Einarson and A.Sundaram, "Platform mounted DVR demonstrated project experience," 5<sup>th</sup> International Transmission and Distribution Conf, Distribution 2000, Brisbane, 1999.

- [4] A.Ghosh and A.Joshi, "A new approach to load balancing and power factor correction in power distribution system," *IEEE Trans. on Power Delivery*, Vol.15, No.1, pp.417-422, 2000.

© 2005 - 2009 JATIT. All rights reserved.

www.jatit.org

- [5] C.G. Hochgraf, "Power inverter apparatus using a transformer with its primary winding connected the source end and a secondary winding connected to load end of an ac power line to insert series compensation, "United States Patent, Number US005905367A, May 1998.

- [6] W.A.Lyon, *Transient Analysis of Alternating–Current Machinaery*, Chapter 2, John Wiley, New York, 1954.

- [7] D.Irwin, Basic Engineering Circuit Analysis. 4<sup>th</sup> Ed., Mac-milan, New York, 1993.

#### **BIOGRAPHY:**

**S.Leela** received her BE degree in Electrical & Electronics Engineering from Bharathidasan University, Trichy in 1990 and she received her ME degree in Power Electronics and Industrial Drives from Sathyabama Institute of Science and Technology, Chennai in the year 2006. She is a research scholar of Bharath University, Chennai. Currently, she is an Assistant Professor at Trichy Engineering College, Trichy. Her interests are in power quality improvement.

**Dr. S.S. Dash** received the ME in Power Systems from U.C.E, Orissa, in 1996. He received the Ph.D. degree in Electrical Engineering from Anna University, Chennai in 2006. Currently, he is a professor at SRM University, Chennai. His research interests include Power Systems, Power Electronics and Power Quality Improvement.