© 2005 - 2013 JATIT & LLS. All rights reserved

ISSN: 1992-8645

www.jatit.org

E-ISSN: 1817-3195

### CONTROL OF TRANSFORMERLESS UNINTERRUPTED POWER SUPPLY FOR UNITY POWER FACTOR AND SINUSOIDAL INDUCTOR CURRENTS

SHAILAJA K<sup>1</sup>, B. UMAMAHESWARI<sup>2</sup>

<sup>1</sup> Research Scholar, Dept. of EEE, Anna University, Tamilnadu, Pin 600025,India, <sup>2</sup>Professor, Dept. of EEE, Anna University, Tamilnadu, Pin 600025,India, E-mail: <sup>1</sup> <u>kshaila 15@yahoo.com</u>, <sup>2</sup> <u>umamahesb@annauniv.edu</u>

#### ABSTRACT

This paper discusses the design of controller for transformerless uninterruptible power supply (UPS), with simultaneous ac and dc loading. The objective of the design is to maintain good regulation of the ac and dc voltages and sinusoidal inductor currents simultaneously. The volt-second balance across the output filter inductor is used to maintain the current in sinusoidal form which is the unique contribution of this paper. Complete analytical design solution is provided for both rectifier and inverter simultaneously. Implementation of the controller requires simple analog circuits. The proposed solution is validated through simulation and experimentation.

# Keywords: Ac And Dc Load, Carrier Based Modulation, Half Bridge Boost Rectifier, Transformerless UPS.

#### 1. INTRODUCTION

Efficiency is one of the important concerns in power electronics equipments. Number of switches and the switching frequency are the major contributing factors to power loss. Boost type converter type topology is best suited for providing better voltage regulation and reduced harmonic distortion. Several works have dealt with modeling, analysis and control of half bridge Boost rectifier[1-5,16-18]. Various configurations of boost converter topologies are presented in [1]. Among these, single phase half bridge voltage doubler boost converter has been a best choice for low cost, massive high power and variable power factor applications [2-4]. The configuration of the half bridge converter topology is expected to have higher efficiency over any converter topologies for UPS applications. It provides voltage doubling and allows transformerless power transfer. The circuit is extensively used in single phase ac line conditioner and frequency changer applications. Many works have been reported in literature in the direction of control of UPS [11-15]

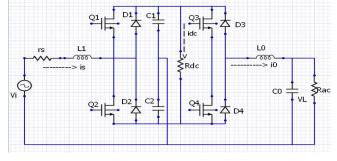

The circuit diagram of the half bridge boost converter also known as transformerless UPS is shown in Figure 1.

Figure.1.Circuit Diagram Of The Transformerless UPS

There are five challenges associated with the transformerless UPS control namely i) to regulate the dc bus voltage ii) to regulate the output ac voltage iii) To maintain input power factor at unity iv) to hold DC bus voltage equally in the two capacitors and v)to hold input inductor and output ac filter currents sinusoidal.

Detailed state space analysis and analytical results related to half bridge boost rectifier efficiency and voltage imbalances are reported in [3].The influence of circuit parameters variation and switching strategy on the boost rectifier's

31<sup>st</sup> December 2013. Vol. 58 No.3

© 2005 - 2013 JATIT & LLS. All rights reserved

| ISSN: 1992-8645 | www.jatit.org | E-ISSN: 1817-3195 |

|-----------------|---------------|-------------------|

|                 |               |                   |

performance and controller design are reported in [2].

A nonlinear carrier based control is proposed in [5] for high power factor boost rectifiers. The technique eliminates input voltage sensing, error amplifier in the current shaping loop and multiplier-divider circuitry. Design of a digital programmable control IC for common neutral half bridge ac-dc-ac converter is presented in [6]. The paper also discusses the inner current loop and the outer voltage loop for ac regulation. A simple analog circuit with complete analytical design solutions is presented for the rectifier in [4]. The paper also illustrates the function of carrier based modulation as an equivalent current loop. An inverse transfer function based zero phase shift notch filter control is proposed for SPWM inverter in [7] where the dc dynamics is kept constant. A four- leg type converter which operates as a rectifier, a battery charger/discharger and an inverter with necessary analysis and design of control schemes is presented in [8].

The analytical equations of the UPS show that ac and dc dynamics are decoupled for voltage regulation. Hence the ac and dc voltage regulations can be dealt separately. However the ac and dc dynamics are coupled for the current dynamics. Hence the design for sinusoidal input and output filter inductor currents should be dealt in the coupled form. This feature is the unique contribution of the proposed paper when compared to the existing literature. In this paper the complete control scheme is presented for regulating the ac and dc bus voltages. The method used for maintaining the unity power factor at the input is extended to maintain the output inductor currents in sinusoidal form. The control functions for both the ac and dc voltage regulations are derived from voltsecond balance equations across the input and output filter inductors respectively. This results in simple analog control functions for both the rectifier and inverter which can be easily implemented.

#### 2. CIRCUIT CONFIGURATION AND MATHEMATICAL MODELLING

The circuit diagram of the transformer less UPS is shown in Figure 1.Vi is the input voltage, L1 is the input inductor, rs is the equivalent series resistance of the inductor, C1 and C2 are the dc link capacitors, Rdc is the dc load resistor, L0 and C0 are the inductance and capacitance of the output filter and Rac is the ac load resistor. Switches Q1 and Q2 correspond to the rectifier portion and Q<sub>3</sub>

and  $Q_4$  correspond to the inverter portion of the UPS.

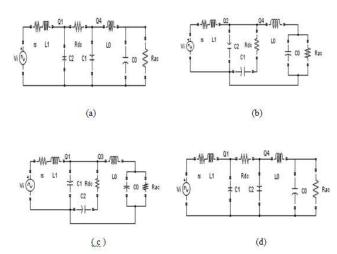

The equivalent circuit diagrams for various switch positions are shown in Figure 2. Operation of the circuit can be explained in four modes as given by Table 1 depending on the ON and OFF conditions of  $Q_1 \& Q_2$  and  $Q_3 \& Q_2$

Q4 as indicated by  $S_1$  and  $S_2$ .

Figure 2. Equivalent circuit diagrams for ON and OFF conditions of the switches (a)  $Q_2$  and  $Q_3$  ON (b)  $Q_2$ and  $Q_4$  ON (c)  $Q_1$  and  $Q_3$  ON (d)  $Q_1$  and  $Q_4$  ON

Table 1: ON-OFF condition of the switches

| <b>Q</b> <sub>1</sub> | <b>Q</b> <sub>2</sub> | $\mathbf{S}_1$ | <b>Q</b> <sub>3</sub> | <b>Q</b> <sub>4</sub> | S <sub>2</sub> |

|-----------------------|-----------------------|----------------|-----------------------|-----------------------|----------------|

| ON                    | OFF                   | 1              | ON                    | OFF                   | 1              |

| OFF                   | ON                    | 0              | OFF                   | ON                    | 0              |

$The dynamic equations in terms \\ of S_1 and S_2 can be given as follows.$

$$L_{1} \frac{di_{s}}{dt} = v_{i} - r_{s}i_{s} + S_{1}v_{c2} - (1 - S_{1})v_{c1}$$

(1a)

$$C_{1} \frac{dv_{c1}}{dt} = -i_{dc} - i_{0}S_{2} + i_{s}(1 - S_{1})$$

(1b)

$$C_{2} \frac{dv_{c2}}{dt} = -i_{dc} - i_{0}(1 - S_{2}) - i_{s}S_{1}$$

(1c)

$$L_0 \frac{di_0}{dt} = S_2 v_{C1} - (1 - S_2) v_{C2} - r_d i_0 - v_l (1d)$$

$$C_0 \frac{dv_l}{dt} = i_0 - i_l \qquad (1e)$$

31<sup>st</sup> December 2013. Vol. 58 No.3

© 2005 - 2013 JATIT & LLS. All rights reserved.

| ISSN: 1992-8645 | www.jatit.org | E-ISSN: 1817-3195 |  |

|-----------------|---------------|-------------------|--|

|                 |               |                   |  |

where  $S_1$  and  $S_2$  to be substituted from Table 1.

Upon replacing  $S_1$  and  $S_2$  by  $d_1$  and  $d_2$ where  $d_1$  is the duty ratio of  $Q_2$  and  $d_2$  is the duty ratio of  $Q_3$ , the average model is obtained as in equations (2a-2e)

$$L_1 \frac{di_s}{dt} = v_i - r_s i_s + d_1 v_{C2} - (1 - d_1) v_{C1}$$

(2a)

$$C_{1} \frac{dv_{c1}}{dt} = -i_{dc} - i_{0}d_{2} + i_{s}(1 - d_{1})$$

(2b)

$$C_1 \frac{dv_{c2}}{dt} = -i_{dc} - i_0 \left(1 - d_2\right) - i_s d_1$$

(2c)

$$L_{0} \frac{di_{0}}{dt} = d_{2}v_{c1} - (1 - d_{2})v_{c2} - r_{d}i_{0} - v_{l}$$

(2d)

$$C_{0} \frac{dv_{l}}{dt} = i_{0} - i_{l}$$

(2e)

#### 2.1 Small Signal Model

For small perturbations in the variables around their nominal values, a linearised small signal model is formed so as to facilitate the controller design.

Let,

$$d_1 = D_1 + \hat{d}_1$$

,  $d_2 = D_2 + \hat{d}_2$ ,

$v_{c1} = v_{c1} + \hat{v}_{c1}$ ,  $v_{c2} = v_{c2} + \hat{v}_{c2}$ ,

$\hat{i}_s = I_s + \hat{i}_s$ ,  $\hat{i}_0 = I_0 + \hat{i}_0$ ,  $v_l = v_l + v_l$

Where D<sub>1</sub>, D<sub>2</sub>, V<sub>c1</sub>, V<sub>c2</sub>, I<sub>s</sub>, V<sub>0</sub> are the nominal

values of the variables,  $\hat{d}_1$ ,  $\hat{d}_2$ ,  $V_{c_1}$ ,  $V_{c_2}$ ,  $\hat{i}_s$ ,  $\hat{i}_0$ ,

$v_l$  are the small perturbations in the corresponding variables and d<sub>1</sub>, d<sub>2</sub>, v<sub>c1</sub>, v<sub>c2</sub>, i<sub>s</sub>, i<sub>0</sub>, v<sub>0</sub> are the respective instantaneous values.

$$L_{1}\frac{di_{s}}{dt} = \hat{v}_{i} - r_{s}i_{s} + \hat{d}_{1}V_{c2} + D_{1}\hat{v}_{c2} - (1 - D_{1})\hat{v}_{c1} + \hat{d}_{1}V_{c1}$$

(3a)

$$C_{1}\frac{d\hat{v}_{c1}}{dt} = -i_{dc} - i_{0}D_{2} - I_{0}d_{2} + (1 - D_{1})\hat{i}_{s} - I_{s}d_{1}$$

(3b)

$$C_2 \frac{\hat{dv}_{C2}}{dt} = -\hat{i}_{dc} - D_1 \hat{i}_s - I_s \hat{d}_1 - \hat{i}_0 (1 - D_2) + I_0 \hat{d}_2 \quad (3c)$$

$$L_0 \frac{d\hat{i}_0}{dt} = D_2 \hat{v}_{c1} + V_{c_1} \hat{d}_2 - (1 - D_2) \hat{v}_{c2} + V_{c_2} \hat{d}_2 - r_s \hat{i}_0 - \hat{v}_l \quad (3d)$$

$$C_0 \frac{\hat{dv}_l}{dt} = \hat{i}_0 - \frac{\hat{v}_l}{R_{ac}}$$

(3e)

Equations (3a) to (3e) describe the small signal model and equation (4) gives the Matrix form

# **3.** PROPOSED CONTROL SCHEME FOR SINUSOIDAL INDUCTOR CURRENTS

Consider the transformerless UPS circuit shown in Figure 1. Assuming similar switching frequency for both converter and inverter circuits, let T be the switching period. Assuming a constant and high switching frequency f(1/T) the duty cycle  $d_1$  and  $d_2$  can be determined by the volt-second balance across the inductors  $L_1$  and  $L_0$  respectively as given by

$$v_i - i_s r_s = v_{c_1} - d_1 \left( v_{c_1} + v_{c_2} \right)$$

(5a)

$$v_l + i_0 r_d = d_2 (v_{c1} + v_{c2}) - v_{c2}$$

(5b)

As per control objective, the inductor current  $i_s$  should be made proportional to the input voltage  $v_i$  for unity power factor and the output inductor current should be sinusoidal with its frequency equal to the output voltage but need not be in phase with it.

Then

$$i_s = K_1$$

(Vmi sin  $\omega_i t$ ) (6a)

and

$$i_0 = K_2 V_{m0} \sin(\omega_0 t + \phi_0)$$

(6b)

Where  $K_1, K_2$  and  $\phi_0$  are constants.

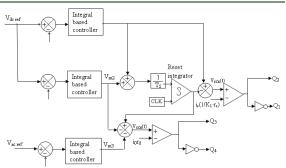

Let us consider three integral based control loops one each for regulating  $v_{C1}$ ,  $v_{C2}$  and  $v_1$

respectively as shown in figure 3. Then  $v_{c1}$ ,  $v_{C2}$  and  $v_1$  of equations (5a) and (5b) can be replaced by corresponding controller outputs  $v_{m1}$ ,  $v_{m2}$  and  $v_{m3}$  respectively for each switching cycle in steady state.

Equations (5a) and (5b) can be rewritten as given by 7a and 7b with  $v_i$  replaced in terms of  $\underline{i_s}$

$$i_{s}\left(\frac{1}{K_{1}}-r_{s}\right)=v_{m1}-d_{1}\left(v_{m1}+v_{m2}\right)$$

(7a)

$$-r_d i_0 = v_{m3} - d_2 (v_{m1} + v_{m2}) + v_{m2}$$

(7b)

The variables  $d_1$  and  $d_2$  can be solved from the equations (7a) and (7b)

<u>31<sup>st</sup> December 2013. Vol. 58 No.3</u>

© 2005 - 2013 JATIT & LLS. All rights reserved.

ISSN: 1992-8645 www.jatit.org

$$d_1 = \frac{v_{m1} - \left(\frac{V_i \sin \omega_i t}{K_1}\right) \left(\frac{1}{K_1} - r_s\right)}{v_{m1} + v_{m2}}$$

(8a)

$$d_{2} = \frac{r_{d}K_{2}v_{0}\sin(\omega_{0}t + \varphi_{0}) + v_{m3} + v_{m2}}{v_{m1} + v_{m2}}$$

(8b)

Equation 8b shows that the dc loop control commands Vm1 and Vm2 influence the duty cycle of the inverter switches for maintaining sinusoidal inductor currents.

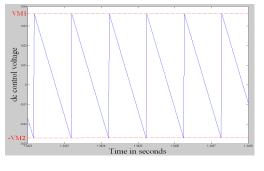

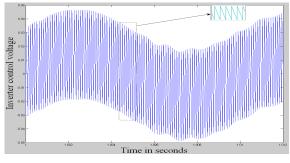

Solving of (8a) & (8b) requires an estimate of K1, K2 and  $\phi_0$ . An alternate solution is to generate the switching pulse using a carrier based approach [4, 9]. Let  $V_{c01}$  and  $V_{c02}$  represent the right hand side of equations 7a & 7b with  $d_1$  and  $d_2$  replaced by t/T. Then

$$\begin{split} V_{CO1}\left(t\right) &= V_{m1} - (V_{m1} + V_{m2}) \ t/T \ ; \ 0 < t < T \eqno(9a) \\ V_{CO2}\left(t\right) &= +V_{m3} + V_{m2} - \ (V_{m1} + V_{m2}) t/T \ ; \ 0 < t < T \end{split}$$

(9b)

It can be easily deduced from 9a and 9b

that,

$$V_{CO1}(t)$$

is equal to  $V_{m1}$  in the beginning of

any interval T (t=0) and will be equal to  $-V_{co1}$  at the

any interval T (t=0) and will be equal to  $-V_{m2}$  at the end of the interval. $V_{COI}(t)$  equals  $i_s(\frac{1}{K_1} - r_s)$  at the

instant t = D<sub>1</sub>T as in equation (7a). Thus switching instant of inverter can be determined by comparing the input current  $i_s(\frac{1}{K_1} - r_s)$  with V<sub>CO1</sub> (t) using a

comparator as shown in Figure 3. Similarly,  $V_{CO2}$  (t) is equal to  $-V_{m2}-V_{m3}$  in the beginning of any interval T and will be equal to  $V_{m1} - V_{m3}$  at the end of the interval.  $V_{CO2}$  (t) equals  $r_d i_0$  at end of  $D_2 T$  as shown in (7b). Thus the switching instant of inverter can be determined by comparing the ac filter inductor current  $-r_d i_0$  with  $V_{CO2}$  (t) with the help of a comparator as shown in Figure 3.

This completes the design of control scheme for sinusoidal inductor currents. The voltage regulation loops are discussed in the following sections.

Figure3. Block diagram of the control scheme

Figure. 4. Control voltage Vco<sub>1</sub>(t)

*Figure. 5. Control voltage Vco*<sub>2</sub>(*t*)

# 4. CONTROLLER DESIGN OF AC/DC VOLTAGE REGULATION

Considering the symmetry of the circuit the following simplifications can be made

$V_{c1} = V_{c2} = V_c$ ,  $\hat{v}_{C1} = -\hat{v}_{C2} = \hat{v}_C$ ,  $D_1=0.5$ ,  $D_2 = 0.5$ . The simplified transfer functions are given as follows,

$$\frac{\hat{v}_{c}(s)}{\hat{d}_{1}(s)} = -\frac{I_{s}}{C_{1}} \left( \frac{s + \left(\frac{r_{s}}{L_{1}} - \frac{V_{c}}{I_{s}L_{1}}\right)}{s^{2} + \frac{r_{s}}{L_{1}} + \frac{0.5}{C_{1}L_{1}}} \right)$$

(10a)

31<sup>st</sup> December 2013. Vol. 58 No.3

© 2005 - 2013 JATIT & LLS. All rights reserved.

| ISSN: 1992-8645 | www.jatit.org | E-ISSN: 1817-3195 |

|-----------------|---------------|-------------------|

|                 |               |                   |

$$\frac{\hat{v}_c(s)}{\hat{d}_2(s)} = -\frac{I_0 L_1 \left(s + \frac{r_s}{L_1}\right)}{s^2 + \frac{r_s}{L_1} s + \frac{0.5}{C_1 L_1}}$$

(10b)

are perfectly sinusoidal with unity power factor. It is observed that the same (power factor being unity and the sinusoidal nature) is maintained over a wide range of operating conditions.

$\hat{\frac{v_0(s)}{\hat{d}_2(s)}} = \frac{2V_c}{\left(s^2 + \left(\frac{R_{ac}r_dC_0 + L_0}{L_0C_0R_L}\right)s + \left(\frac{R_{ac} + r_d}{L_0C_0R_L}\right)\right)L_0C_0}$ (11)

In the steady state, the effects of  $\hat{d}_1 \& \hat{d}_2$  on  $\hat{v}_c$  and  $\hat{v}_0$  are tabulated in table 2.

Table 2: Variation of  $\hat{v}_0(s) \& \hat{v}_c(s)$  with  $\hat{d}_1 \& \hat{d}_2$

|             | $\hat{v}_c$                             | $\hat{v}_0$                         |

|-------------|-----------------------------------------|-------------------------------------|

| $\hat{d}_1$ | $\frac{I_s r_s}{0.5} - \frac{V_c}{I_s}$ | 0                                   |

| $\hat{d}_2$ | $\frac{I_0 r_s}{0.5} L_1 C_1$           | $\frac{2V_{c}R_{ac}}{R_{ac}+r_{d}}$ |

It can be observed from table 2 that the effect of  $\hat{d}_2$  on  $\hat{v}_c$  is insignificant when compared to the effect of  $\hat{d}_1$  on  $\hat{v}_c$  due to the product of  $r_s$ ,  $L_1$  and  $C_1$ . This results in two decoupled transfer functions as given by equations (10a) and (11).

Simple Proportional-integral control schemes can be employed for both the converter as well as the inverter. The transfer function of the controller is given by the equation (12). The proportional gain and the integral gain of the controller are selected through root locus technique.

$$C(s) = \frac{K_{P}s + K_{I}}{s}$$

(12)

#### 5. SIMULATION AND EXPERIMENTAL RESULTS

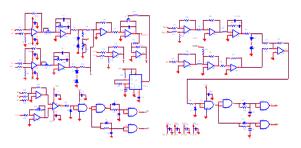

The UPS is designed with parameters shown in table 3. The operational amplifier implementation of control circuit is shown in figure 6. The complete hardware setup is shown in figure

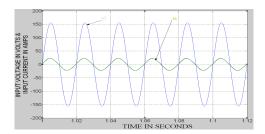

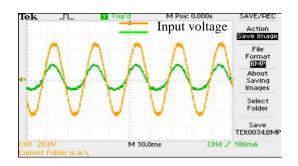

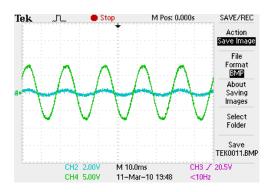

Figure 8 shows the input voltage and current waveforms in steady state. The waveforms

| f <sub>SW</sub> | 10KHz   |

|-----------------|---------|

| fi              | 50Hz    |

| L1              | 1mH     |

| rs              | 0.2 Ω   |

| C1              | 2200 µF |

| C2              | 2200 µF |

| Rdc             | 95 Ω    |

| L <sub>0</sub>  | 1mH     |

| $C_0$           | 210 µF  |

| R <sub>ac</sub> | 80 Ω    |

Figure.6.Circuit diagram of the controller

Figure .7 Hardware setup

Figure 8.Input voltage  $(V_i)$  & input current  $(i_s)$

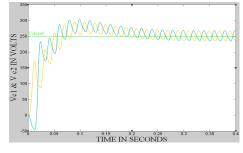

The rectifier output transient and steady state voltage across the two dc link capacitors is

31<sup>st</sup> December 2013. Vol. 58 No.3

© 2005 - 2013 JATIT & LLS. All rights reserved.

| ISSN: 1992-8645 www.jatit.org | E-ISSN: 1817-3195 |

|-------------------------------|-------------------|

|-------------------------------|-------------------|

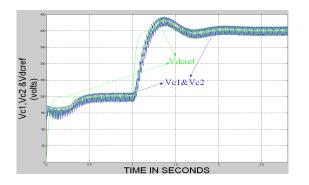

shown in figure 9a. The voltages settle to any desired value over a wide range of input voltage, reference voltage and load current. It is possible to further reduce the magnitude of ripple in steady state

Figure.9a. V<sub>C1</sub> & V<sub>C2</sub>

Rectifier response for a step change of 200 volt (from 200 volt to 400 volt) in the dc reference is shown in figure 10b. It can be observed from Figure 9b that Vc1 and Vc2 have reached the set voltage with a small overshoot and undershoot.

Figure.9b.  $V_{C1}$  &  $V_{C2}$  for a step change in Vdc reference

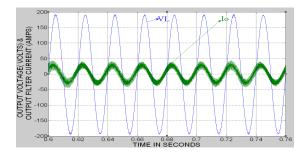

The output voltage and the output filter current in steady state are shown in figure 10. The Voltage and the current are sinusoidal. However the harmonic distortion in the output inductor current is higher than the input .

Figure.10. Output voltage  $(V_l)$  & output filter Current $(i_0)$

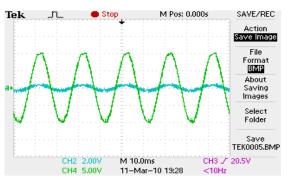

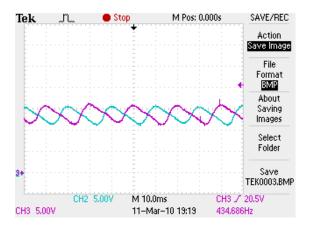

Experimental results are shown in figures 11a and 11b. Experimental results match with the results obtained through simulation. Figures 11a-11c show the input voltage and input current waveforms for varying converter parameters, input voltage and reference. Input current is maintained sinusoidal and the power factor is near unity. Rectifier output is shown in figures 12a and 12b. It can be observed that rectifier has very low ripple. The rectifier output reaches any set value.

Figure.11a.Input voltage  $(V_i)$  & input current  $(i_s)$

Figure 11 b. Input voltage  $(V_i)$  & input current  $(i_s)$

Figure 11 c. Input voltage  $(V_i)$  & input current  $(i_s)$

31st December 2013. Vol. 58 No.3

© 2005 - 2013 JATIT & LLS. All rights reserved.

ISSN: 1992-8645

www.jatit.org

M Pos: 0.000s SAVE/REC Tek m Action Save Image File Forma BMP About Saving Select Folder Save TEK0026.BMP CH2 20.0V M 10.0ms

Fig.12a .Rectifier output (voltage across  $V_{C1}$  and  $V_{C2}$ )

Figuer.12b. Rectifier output (voltage across  $V_{C1}$  and  $V_{C2}$ )

#### 6. CONCLUSION

The dynamic equations describing the functioning of the UPS are presented .The control schemes are derived from volt-second balance of the input and output filter inductors. The regulation of ac and dc voltages is presented using small signal models. The transient and steady state performances are simulated for wide range of line and load variations. The switching pulses are generated with simple comparators and integrators. The performance of the controlled UPS is studied in simulation as well as experimentation. The method proposed in this paper has ensured sinusoidal input and output inductor currents and proper regulation of the ac and dc voltages.

#### REFERENCES

- A.Pandey, B.Singh, D.P.Kothary [1] "Comparative evaluation of single-phase unity power factor ac-dc Boost converter topologies" IE(I) Journal – EL, July 2003.

- Felipe J.C. Padilha and etal"Modelling and [2] control of the half bridge voltage-doubler

converter" IEEE Boost international symposium on power electronics,2006

- S. Chattopadhyay, V. Ramanarayanan, and V. [3] Jayashankar, "Predictive switching modulator for current mode control of high power factor boost rectifier," IEEE Trans. Power Electron., vol. 18, no. 1, Jan. 2003, pp.114-123.

- [4] Rajesh Ghosh and G. Narayanan "A Simple Analog Controller for Single-Phase Half-Bridge Rectifier" IEEE Trans. Power Electronics, vol. 22, No. 1, Jan. 2007, pp. 186-198.

- D. Maksimovic, Y. Jang, and R. Erickson, [5] "Nonlinear-carrier control for high- powerfactor boost rectifiers," IEEE Trans. Power Electron., vol. 11, no. 4, July 1996, pp. 578-584.

- [6] Ming-Fa Tsai etal "Design of a digital programmable control IC for common-neutral half bridge bilateral AC-DC-AC converters", IEEE Power electron. and motion control conf., IPEMC 2004, 4-16 Aug. 2004, pp 1647-1653.

- [7] Kai Zhang, Yong kang etal "Direct repetitive control of SPWM inverter for UPS purpose" IEEE Trans. Power Electronics, vol. 18, No. 3, May 2003, pp 784-792.

- Jae-kyu prk, Jung-Min kwon etal "High -[8] Performance transformerless online UPS" IEEE Trans. Industrial Electronics, vol. 23, No. 8, Aug 2008, pp 2943-2953.

- [9] Oiao and K. M. Smedley, "Unified constantfrequency integration control of three-phase standard bridge boost rectifiers with powerfactor correction," IEEE Trans. Ind. Electron., vol. 50, no. 1, Feb. 2003, pp. 100-107.

- [10] Kishor, D.Subbarayudu, G. and S.Sivanagaraju, " comparison of full bridge and two inductor boost converter systems," journal of theoretical and applied information technology, Vol. 34, no. 2, Dec. 2011, pp. 118-124.

- [11]M.Karpagam, N.Devarajan, "implementation of soft switched converters for high power Application," Journal of Theoretical and Applied Information Technology, 2005, pp52-57.

- [12] S. B.Bekiarov, Emadi A, "A New On-Line Single-phase to Three-phase UPS Topology with Reduced Number of Switches," Power Electronics Specialist conference, PESC'03, June 15-19 2003, vol.1, pp 451 – 456.

- [13] Carlos Augusto Ayres and Ivo Barbi, "A Family of Converters for UPS Production

31<sup>st</sup> December 2013. Vol. 58 No.3

© 2005 - 2013 JATIT & LLS. All rights reserved

| ISSN: 1992-8645 | www.jatit.org | E-ISSN: 1817-3195 |

|-----------------|---------------|-------------------|

|                 |               |                   |

Burn-In Energy Recovery" *IEEE Trans. on power Electron.*, vol.12, no. 4, july 1997, pp.614-615. [14] Grundling, H.A. Carati,Pinheiro. J.R., " A robust model reference adaptive controller for UPS applications," *Intl. conf. Indus. Electron. and Control and Instrumentation*, IECON 97, 9-14 Nov 1997, vol.2, pp 901 – 905.

- [15] Busan, Hasall JGmiirciigil, "A PI-Type Self-Tuning Fuzzy Controller for Dc-\Dc Boost Converters," The 30th Annual Conf. of the IEEE Indus. Electron., Nov 2-6, 2004, pp 209-214.

- [16] Handy Fortin Blanchette, Tarek Ould-Bachir and Jean Pierre, "A State-Space Modeling Approach for the PGA-Based Real-Time Simulation of High Switching Frequency Power Converters," *IEEE trans. Ind. Electron.*, vol. 59, no. 12, December 2012, pp. 4555-4567.

- [17] Fellipe S. Garcia, Antenor Pomilio, and Giorgio Spiazzi, "Modeling and Control Design of the Interleaved Double Dual Boost Converter," *IEEE trans. ind electron*, vol. 60, no.8, August 2013. pp. 3283-3290.

- [18] Yongchang Zhang, , Zhengxi Li, , Yingchao Zhang, Wei Xie, Zhengguo Piao, and Changbin Hu, "Performance Improvement of Direct Power Control of PWM Rectifier With Simple Calculation," *IEEE trans. power electron.*, vol. 28, no. 7, July 2013, pp. 3428-3437.