20<sup>th</sup> July 2013. Vol. 53 No.2

© 2005 - 2013 JATIT & LLS. All rights reserved

ISSN: 1992-8645

www.jatit.org

E-ISSN: 1817-3195

# A DESIGN OF ANALOG VOLTAGE-MODE MULTIPLIER FOR UHF RFID PASSIVE IN 0.18UM CMOS PROCESS

<sup>1</sup>SMAIL HASSOUNI, <sup>2</sup>HASSAN QJIDAA, <sup>3</sup>MOHAMED LATRACH

<sup>1,2</sup> Faculté des sciences Dhar El Mehraz Laboratoire d'Electronique Signaux – Systèmes et Informatique(LESSI) Fès Morocco

<sup>3</sup>Groupe Radio & Hyperfréquences ESEO, 4 Rue Merlet de la Boulaye, BP 30926, 49009

Groupe Radio & Hyperfrequences ESEO, 4 Rue Merlet de la Boulaye, BP 30926, 49009 Angers, France

E-mail: <sup>1</sup>sm3il 2000@hotmail.fr

#### ABSTRACT

In this paper a "Low Voltage, Low Power, High Speed and High Linearity-CMOS Analog Multiplier for Modem ASK is proposed". The multiplier circuit is implemented in 180nm CMOS technology. It can be operated even at low Supply voltage VDD=0.9V. Band width of operation is about 4.10MHz, which is suitable for high frequency/high speed applications. This device modulates an analog carrier signal to encode digital information, and also demodulates such a carrier signal to decode the transmitted information. The goal is to produce a signal that can be transmitted easily and decoded to reproduce the original digital data.

**Keywords:** Modulator ASK; ASK demodulator; Multiplier; Physical design; radio frequency identification (RFID).

#### 1. INTRODUCTION

Analog multiplier, Figure 1 is an important basic building block in communication systems like analog signal processing systems; for example frequency mixers, variable gain amplifiers, adaptive filters, phase-locked loop, amplitude modulators, frequency doublers, rectifiers and demodulators etc. It is necessary to design an analog multiplier circuit which is suitable for low power, low voltage and high speed applications with better linearity.

Figure 1.Basic Multiplier Symbol

Depending on the input/output, analog multipliers can be classified as, Voltage Mode Multipliers [1] and Current Mode Multipliers [2].

And also depending on the circuit configuration it can be classified as:

- Single balanced (2-quadrant), and

- Double balanced (4-quadrant) multipliers.

- Quadrant based classification of multipliers is as follows:

- One-quadrant multipliers: Inputs are of the same phase

- Two quadrant multipliers: Opposite voltage can be added to either of the input

- Four quadrant multipliers: Opposite voltage can be added to both the inputs

#### 2. FOUR-QUADRANT MULTIPLIERS USING SERIES CONNECTED TRANSISTORS

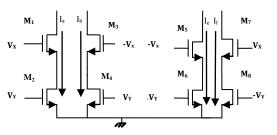

A voltage mode four quadrant analog multiplier based on a basic NMOS differential amplifier[1] can produce the output signal in voltage form can be constructed using four one-quadrant multipliers or by using two two-quadrant multipliers as shown in Figure. 2.

Figure 2. Four-Quadrant Multiplier

### Journal of Theoretical and Applied Information Technology

20th July 2013. Vol. 53 No.2

© 2005 - 2013 JATIT & LLS All rights res

|                 | © 2003 - 2013 JATTI & LLS. All fights reserved     | JATIT             |

|-----------------|----------------------------------------------------|-------------------|

| ISSN: 1992-8645 | www.jatit.org                                      | E-ISSN: 1817-3195 |

|                 | the four-quadrant multiplier with series connected |                   |

$$I_{a} = \sqrt{I_{d_{1}}} * \sqrt{I_{d_{2}}}$$

(2.1)

$$I_{b} = \sqrt{I_{d_{3}}} * \sqrt{I_{d_{4}}}$$

(2.2)

$$I_{total_{1}} = I_{a} - I_{b} \tag{2.3}$$

$$I_{a} = k (v_{gs_{1}} - v_{th})(v_{gs_{2}} - v_{th})$$

(2.4)

$$I_{a} = k (v_{x} - v_{0} - v_{th})(v_{y} - v_{th})$$

(2.5)

$$I_{a} = k (v_{x} - a)(v_{y} - b)$$

(2.6)

$$I_{b} = k (v_{gs_{3}} - v_{th})(v_{gs_{4}} - v_{th})$$

(2.7)

$$I_{b} = k (-v_{x} - v_{0} - v_{th})(v_{y} - v_{th})$$

(2.8)

$$I_{b} = k (-v_{x} - a)(v_{y} - b)$$

(2.9)

$$I_{total_{1}} = 2kv_{x}(v_{y} - b)$$

(2.10)

$$I_{e} = \sqrt{I_{d_{5}}} * \sqrt{I_{d_{6}}}$$

(2.11)

$$I_{f} = \sqrt{I_{d_{7}}} * \sqrt{I_{d_{8}}}$$

(2.12)

$$I_{total_2} = I_e - I_f \tag{2.13}$$

$$I_{e} = k (v_{gs_{5}} - v_{th})(v_{gs_{6}} - v_{th})$$

(2.14)

$$I_{e} = k (-v_{x} - v_{0} - v_{th})(-v_{y} - v_{th}) \quad (2.15)$$

$$I_{e} = k (-v_{x} - a)(-v_{y} - b)$$

(2.16)

$$I_{f} = k (v_{gs_{7}} - v_{th})(v_{gs_{8}} - v_{th})$$

(2.17)

$$I_{f} = k (v_{x} - v_{0} - v_{th})(-v_{y} - v_{th})$$

(2.18)

$$I_{f} = k (v_{x} - a)(-v_{y} - b)$$

(2.19)

$$I_{total_2} = -2kv_x (-v_y - b)$$

(2.20)

$$I_{total} = I_{total_1} + I_{total_2}$$

(2.21)

$$I_{total} = 4kv_x v_y \tag{2.22}$$

The above equation (2.22) shows the output of four-quadrant multiplier which is independent of threshold voltage and depends on aspect ratio (W/L) of the transistors. In the following section let us analyze the basic voltage mode multiplier using the four-quadrant multiplier with series connected transistors.

#### **3. BASIC VOLTAGE MODE MULTIPLIER**

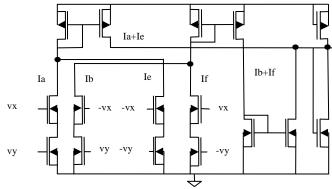

Figure 3 shows the basic voltage mode multiplier structure which is constructed using four quadrant multiplier [5-6] with series connected transistors.

Figure 3.Basic Voltage Mode Multiplier Structure

Since it has to operate in all the quadrants, output of Vx\*Vy and -Vx\*-Vy are cross connected to get the total current Itotal1 and similarly the output of -Vx \*Vy and Vx\*-Vy are cross connected to get the total current Itoatl2.

#### **4. SIMULATION RESULTS**

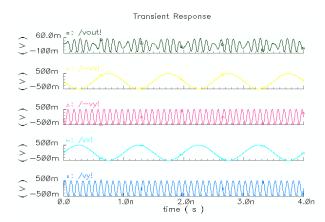

The simulation results of schematic design for basic multiplier are presented. Different Analysis is performed to check the performance of the multiplier. Vx and -Vx 500mv, 1GHZ, Vy and -Vy 500mv, 10GHZ .the power consumed by the basic multiplier is 430.44µW

Figure 4. Transient Analysis Of Basic Multiplier

## Journal of Theoretical and Applied Information Technology

20<sup>th</sup> July 2013. Vol. 53 No.2 © 2005 - 2013 JATIT & LLS. All rights reserved

ISSN: 1992-8645 Ø.ØØ  $\frown -100$ ₽ ₽ –200 -300 -2Ø.Ø ₽ -7Ø.Ø -120 1ØØK 1ØØM 1M 1ØM 1G 1ØG 1ØØG freq (Hz)

Figure 5. Ac Analysis Of Basic Multiplier

5. MULTIPLIER AS DEMODULATOR

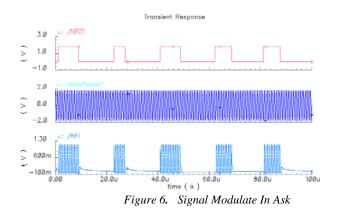

Multiplier can be used as an ASK demodulator in

The new structure proposed as shown in Figure 7.

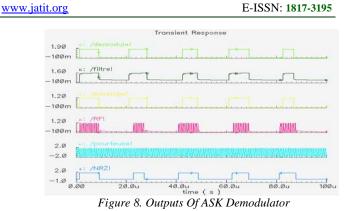

Figure 8 shows the output of proposed ASK demodulator circuit.

Figure 7. The Proposed ASK Demodulator

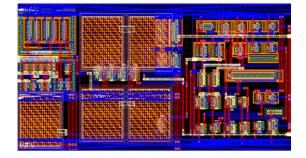

Figure 9. Layout Of The Ask Demodulator

#### 6. CONCLUSION

In this paper a "Low Voltage, Low Power, High Speed and High Linearity-CMOS Analog Multiplier for Modem ASK is proposed". The multiplier circuit is implemented in 180nm CMOS technology with minimum transistor sizes (W/L=400nm/180nm). It can be operated even at low Supply voltage VDD=0.9V. Band width of operation is about 4.10MHz, which is suitable for high frequency/high speed applications.

#### 7. ACKNOWLEDGMENT

This work was supported by: the National Center of Research Scientifique and Technique (CNRST Maroc) under the TIC R&D program.

#### **REFRENCES:**

Boonchu B., Surakampontorn W., "A fourquadrant analog multiplier using basic differential pair", Proceedings of 2004 IEEE Region 10 Conference, Vol. 4, pp.290-293, Nov., 2004.

## Journal of Theoretical and Applied Information Technology

<u>20<sup>th</sup> July 2013. Vol. 53 No.2</u>

© 2005 - 2013 JATIT & LLS. All rights reserved.

| ISSN: 1992-8645 | www.jatit.org | E-ISSN: 1817-3195 |

|-----------------|---------------|-------------------|

|                 |               |                   |

- [2] A Naderi, H Majarrad, H Ghasemzadeh, "Four Quadrant CMOS Analog Multiplier Based on new Current Suarer circuit with high speed", IEEE European Conference, pp 282-287,May 2009.

- [3] Boonchu B., Surakampontorn W., "CMOS voltage-mode analog multiplier", Proceedings of 2006 IEEE International Symposium on Circuits and Systems, pp. 21–24, May, 2006.

- [4] Boonchu B., Surakampontorn W., "A new NMOS four-quadrant analog multiplier", Proceedings of 2005 IEEE International Symposium on Circuits and Systems, Vol. 2, pp.1004 –1007, May, 2005.

- [5] Li Z., Chen C., "Low-power low-noise CMOS analogue multiplier", IEEE Proceedings Circuits, Devices and Systems, Vol. 153, No. 3, pp. 261–267, June 2006.

- [6] Zhangcai Huang, Yasuaki Inoue, Hong Yu and Quan Zhang, " A Wide Dyanamic Range Four Quadrant CMOS Analog Mulitplier using Active Feedback", APCCAS 2006,pp 708-711.

- [7] Yuan Hsiao Sh., Yu Wu Ch.; "A 1.2 V CMOS Four-Quadrant Analog Multiplier" IEEE International Symposium on Circuits and Systems, Hong Kong, (June 9 - 12 1997).

- [8] S. A. Mahmoud," Low voltage Low Power Wide Range Fully Differential CMOS Four-Quadrant Analog Multiplier", IEEE International Midwest Symposium on Circuits and Systems, MWCAS2009, in Cancún, México, pp.130-133, August 2-5, 2009.