10<sup>th</sup> February 2013. Vol. 48 No.1

© 2005 - 2013 JATIT & LLS. All rights reserved.

ISSN: 1992-8645

<u>www.jatit.org</u>

E-ISSN: 1817-3195

# FPGA-BASED DESIGN ON REAL-TIME TOW STAIN DETECTION

# <sup>1,2</sup>JIAN-XIN HUANG, <sup>1</sup>YU-TING TANG, <sup>1</sup>KUN-CHI WANG, <sup>2</sup>CONG-TAO ZHAO, \*YONG-JIE YANG

School of Electronics and Communication, Nantong University 1

Nantong Cellulose Fibers Co., Ltd.<sup>2</sup>

Nantong, Jiangsu, China

\* Corresponding author, E-mail: <u>yang.yj@ntu.edu.cn</u>

#### ABSTRACT

This paper introduces a tow stain detection method based on FPGA. To capture moving images through the line scanning CCD in real time and to design algorithms according to the different characteristics on the tow and stains. Then download it to FPGA development board running and debugging. Finally, displayimages on PC through the video conversion module. The experiments show that this design can effectively detect the stains on the running tow with high speed. It also has good stability and high error detection rate.

Keywords: FPGA; CCD; Stain Detection

#### 1. INTRODUCTION

FPGA (Field Programmable Gates Array) is the further development of programmable devices, such as PAL, GAL, CPLD and so on. FPGA device is a kind of high density digital integrated circuit configurating and defining on site according to the requirements of the system by the user. Miniaturization, convenient, low power consumption, programmable, fast, practical and some other advantages make it has been widely used in recent years[1]. It appears as a semi-custom circuit in Application-specific Integrated Circuit (ASIC) field, not only solving the shortcomings of the original custom circuit but also overcoming the limit of gate numbers of the existing programmable devices[2].

FPGA development board is able to meet the need of long-running production line testing with low-powerchips. Besides it would not be affected even under uninterrupted operation, which ensures the accuracy of the judgments and the speed of the operation.

#### 2. STAIN DETECTION FRAMEWORK DESIGN

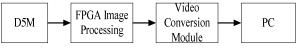

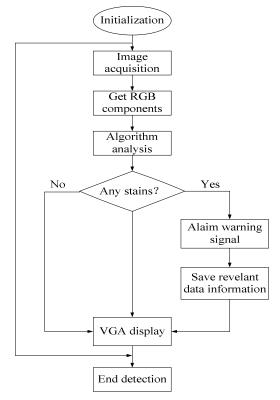

The overall framework of tow stain detection is shown in Figure 1.

The procedures of testing are as follows. The line scanning CCD(D5M) captures real-time images first. And then FPGA controller processes the collected data with the inside algorithm. Once detecting stains, FPGA alarms a signal and controls the VGA to pause for 6 seconds, at the same time records the second seconds' image information and transfers the image to real-time display on PC through the video conversion module. Staffs can do some follow-up processings according to the detection screen or the saved data information.

Figure 1. The Overall Framework Of Tow Stain Detection

# 3. SOFTWARE DESIGN

#### 3.1 Algorithm Design

We get the image with a black stain on it and save as a BMP format file. Camparing and analysing the stain's and the tow's RGB components.

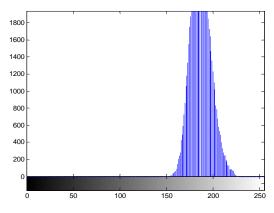

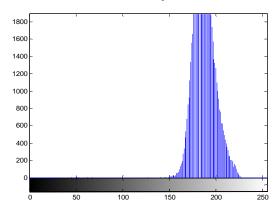

Figure2 is the gray level histogram of a image without any stains, while Figure3 is the gray level histogram with a black stain on it.

# Journal of Theoretical and Applied Information Technology

<u>10<sup>th</sup> February 2013. Vol. 48 No.1</u> © 2005 - 2013 JATIT & LLS. All rights reserved<sup>-</sup>

| ISSN: 1992-8645 | www.jatit.org | E-ISSN: 1817-3195 |

|-----------------|---------------|-------------------|

|-----------------|---------------|-------------------|

By comparison of the two images, we can find that for the black stain the B component values in a range between 25 to 90 while the background(tow) values more than 150.

Figure2. Gray Level Histogram Of A Image Without Stains Under B Component

Figure3. The Image's Gray Level Histogram With A Black Stain Under B Component

Therefore, using a simple threshold segmentation algorithm[3] can isolate the black stain from tow. Threshold function can be expressed as follows:

$$\mathbf{f}(\mathbf{x}) = \begin{cases} 255 & x \ge T \\ 0 & x < T \end{cases}$$

Where T is the selected threshold.

For example, when dealing with black stain in the program, we set the parameter TH= 12'h90 under the B component.

Dealing with other stains, we take a similar approach, implement these algorithms in the program and download it to the FPGA development board.

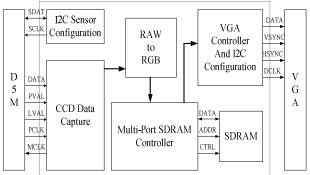

# 3.2 FPGA Design

Most FPGA designs use modular ideas[4], by which a complex system can be divided into a number of small and easily manageable units. The main modules of stain detection are shown in Figure 4.

Figure 4. FPGA Modular Design

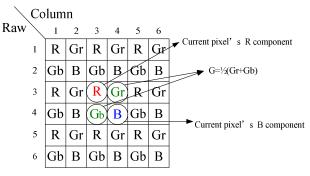

Image Acquisition Module: D5M scans images from left to right and returns to the left to scan the next line when a line's pixels are all scanned. Each pixel's RGB values is expressed as 2\*2 grid square which is shown in Figure5: where R is the value of the current pixel's R component and B is the value of the current pixel's B component while G is the average of Gr and Gb[5][6].

Figure 5. RGB Component Diagram Of D5M

2)I2C Control Module:CCD part is under the control of I2C mode. I2C (Inter-Integrated Circuit )bus is a two-wire serial bus(data and clock)[7]. It's used to connect the microcontroller and its peripherals. The required clock of CCD module is generated by I2C, while CCD Data Capture module generates the first clock that D5M requires. The acquired images can be displayed on VGA when converted to RGB formats.

3)RAW to RGB module: the Raw format is converted to RGB format in this part.And designing a detection algorithm according to the relative characteristics of the tow and stains.At the same time Generating an alarm signal to video

# Journal of Theoretical and Applied Information Technology

© 2005 - 2013 JATIT & LLS. All rights reserved.

| ISSN: 1992-8645                                                                           | <u>www.jatit.o</u> | org                   |          |             | E-ISSN: 1 | 817-3195 |

|-------------------------------------------------------------------------------------------|--------------------|-----------------------|----------|-------------|-----------|----------|

| conversion module to save the image in                                                    | formation          | // Virtical Parameter |          | (Line)      |           |          |

| timely.                                                                                   |                    | para                  | meter    | V_SYNC_CYC  | =         | 3;       |

| We use Linebuffer in this module which<br>is shift register altshift_taps. Shiftin is the | , , ,              | para                  | meter    | V_SYNC_BAC  | K=        | 38;      |

| the output is shiftout.                                                                   | 1                  | para                  | meter    | V_SYNC_ACT  | =         | 1024;    |

| altshift_taps_component.lpm_type="alt                                                     | shift_taps         | para                  | meter    | V_SYNC_FROM | NT=       | 1;       |

| ",                                                                                        |                    | para                  | meter    | V_SYNC_TOT  | AL=       | 1066;    |

| altshift_taps_component.number_of_taps = 3,                                               |                    | // Start Offset       |          |             |           |          |

| altshift_taps_component.tap_distance =                                                    | 1280,              | Para                  | meter X  | START       |           |          |

| altshift_taps_component.width = 12;                                                       |                    |                       | =H_SY    | NC_CYC+H_SY | NC_BAC    | K;       |

| The mentioned program above illust                                                        |                    | Para                  | meter Y_ | START       |           | IZ .     |

parallel output lines (number\_of\_taps) is 3 and the width(tap\_distance) is 1280. Each pixel is represented with 12 bits wide. That is, outputting 3 lines and 1 row together and after 1280 clock outputting an image with 3 integral lines.

Realizing the designed algorithms in this module and down program to the FPGA development board.To get the best threshold and accuracy on the basis of multiple experimental debugging.

4)SDRAM Control Module:In this experiment we choose DE2\_70 as FPGA development board.There are two 32MB-SDRAM on DE2\_70[8].Gr and B components are stored in the first SDRAM and the Gr and R components are stored in the second one.

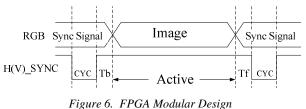

5)VGA Control Mode: VGA displays images in real time with line by line scanning mode, including line scanning and field scanning[9].

As is shown in Figure6, the synchronizing signal includes the back and the front part and the logic low part between them[10][11]. Some parameters in the program are as follows:

| // Horizo | ntal Parameter | ( Pixel | )     |

|-----------|----------------|---------|-------|

| parameter | H_SYNC_CYC     | =       | 112;  |

| parameter | H_SYNC_BAC     | K=      | 248;  |

| parameter | H_SYNC_ACT     | =       | 1280; |

| parameter | H_SYNC_FRO     | NT=     | 48;   |

| parameter | H_SYNC_TOT.    | AL=     | 1688; |

=V\_SYNC\_CYC+V\_SYNC\_BACK; We set the line counter and field counter separately.Line scan is starting when line counter equals X\_START.And once the entire line is scanned over continues scanning the next line.Field scan is the same as line scan.

Figure7 gives the software flowchart:

#### Figure7. Software Flowchart

# 4. THE SIMULATION AND TESTING

We choose Altera's software QuartusII10.0 to synthesize the design and Modelsim-Altera to

# Journal of Theoretical and Applied Information Technology

| 10 <sup>th</sup> | Feb | oruary | 20 | Vol. | 48 | No.1 |

|------------------|-----|--------|----|------|----|------|

| <br>             |     |        |    | <br> |    |      |

© 2005 - 2013 JATIT & LLS. All rights reserved

|                           |               | 111.01            |

|---------------------------|---------------|-------------------|

| ISSN: 1992-8645           | www.jatit.org | E-ISSN: 1817-3195 |

| · 1 · 1 · · · · · · · 1 1 |               |                   |

simulate. The design is tested by using DE2\_70 as the FPGA development board.

The specific steps that QuartusII10.0 calls modelsim6.5 to simulate are as follows[12][13]:

(1)Selecting Modelsim-Altera as the simulation tool before the new project is finished.

(2)Set the path of modelsim.exe:ools->options->EDA tools options(usually in modelsim installation directory under win32 folder).

(3)After the project is compiled, creating a test file:processing->start->start test bench template writer.This file lies in the simulate/modelsim folder

of the project with suffix vt.Open and complete the test file.

(4)Follow the steps that assignment->setting->EDA tools setting->simulation->complie test bench to select complie test bench and click test bench.

(5)Finally clicking tools->run EDA simulate tool->EDA RTL simulation that can successfully call modelsim simulation.

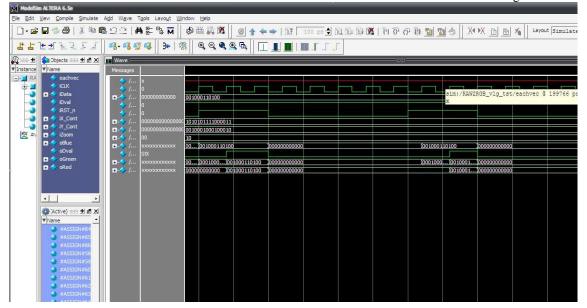

For the entire system, we give each module a separate simulation fist and then take the joint testing[14]. The main algorithm module RAW2RGB's simulation is shown in Figure8.

Figure8. The Simulation Of RAW2RGB Module

We can see the output waveform agrees with the design requirements and achieves the original goals.

Debugging the entire system in production line. The production line's speed is up to 10m/s and the stain's size is only 5mm2.The test results show that the design can detect stains quickly and efficiently. The system functions stable and at the same time cannot be affected by the external environment.

# 5. SUMMARIZE

Because of its short design cycle, high reliability, fast function speed and the superiority of the cost, FPGA has become the fastest-growing category in the electronic components industry[15].

This paper takes full account of the tow and the stains characteristics, the production line's fast speed, the request high accuracy and the changing environment, designs a tow stain detection system based on FPGA technology. It not only simplifies hardware design, improves production efficiency and automation level, but also reduces the waste of social labor, which has a good application prospect.

#### **REFERENCES:**

- [1] Ji Zhicheng, Gao Chunneng. FPGA Digital Signal Processing Design Tutorials-System Generator Primary Materials.Xi'An:Xidian University Press,2008.2.

- [2] Liu Binkai, Yong Shaowei. Research on Design Method for Digital Signal Processing System Based on System Generator. Ship Electronic Engineering, 2010, 30(1).

- [3] Ostu N. "A threshold selection method from gray-level histograms," IEEE Transactions on

|      | © 2005 - 2013 JATIT                                                                                                                                                                                                                                             | & LLS. All rights reserved. |                   |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|-------------------|

| ISSN | : 1992-8645 <u>www.j</u> :                                                                                                                                                                                                                                      | atit.org                    | E-ISSN: 1817-3195 |

|      | Systems, Man, and Cybernetics, vol. 9, no. 1 1979.                                                                                                                                                                                                              | ,                           |                   |

|      | Liu Qiang.The Study on Design Method o<br>SystemC[J]. Modern Electronics Technique<br>2005(9).                                                                                                                                                                  |                             |                   |

|      | L Shi, G Jin, Y An and H Y Tian, "Research or<br>a mechanical interleaving stitching method o<br>CCDs for remote sensing camera," Infrared<br>vol. 30, No. 1, pp. 12-15, Jan 2009.                                                                              | f                           |                   |

|      | TRDB_D5M_UserGuide,http://wenku.baidu.co<br>m/view/b15c9f00cc175527072208ad.html                                                                                                                                                                                | )                           |                   |

|      | B. Hallgren, H.Boterenbrood, H.J. Burckhard<br>H.Kvedalen, "The Embedded Local Monito<br>Board (ELMB) in the front-end I/O Contro<br>System", ATLAS DCS conference papers.                                                                                      | r                           |                   |

|      | Altera Corp, DE2-70 Development and Education Board: User Manual, 2008.                                                                                                                                                                                         | 1                           |                   |

|      | Ping-Sing Tsai, Tinku Acharya, Ajay K.Ray<br>Adaptive Fuzzy Color Interpolation [J]. Journa<br>of Electronic Imaging, 2002, 11(3).                                                                                                                              |                             |                   |

|      | Wu Maocun, "FPGA-based power system<br>harmonic detection," Shandong University o<br>Science and Technology, 2002.                                                                                                                                              |                             |                   |

|      | JS. Yu et.al., "The Development of a 2.6 incl<br>VGA System on Panel," SID Int'l Symposium<br>Dig. Tech. Papers, vol. 37, pp. 224-226, June<br>2006.                                                                                                            | 1                           |                   |

| [12] | ModelSim-Altera,http://wenku.baidu.com/view/bebf751bff00bed5b9f31d60.html                                                                                                                                                                                       | 7                           |                   |

| [13] | The simulation data of Altera_Modelsim<br>http://wenku.baidu.com/view/b015ed02de80d4<br>d8d15a4f40.html                                                                                                                                                         |                             |                   |

|      | Xiao Yanhong, "Summary of power system<br>harmonic detection," Power System<br>Technology. vol. 26, pp. 61-64, 2002.                                                                                                                                            | 1                           |                   |

|      | N. Lashkarian, E. J. Hemhill, H. Tarn, H<br>Parekh and C. Dick "Reconfigurable digita<br>front-end hardware for wireless base-station<br>transmitters: Analysis, design and FPGA<br>implementation", IEEE Trans. Circuits Syst. I<br>Reg. Papers, vol. 54, 2007 | 1<br>n<br>A                 |                   |