#### Journal of Theoretical and Applied Information Technology

15<sup>th</sup> July 2011. Vol. 29 No.1

© 2005 - 2011 JATIT & LLS. All rights reserved

ISSN: 1992-8645 <u>www.jatit.org</u> E-ISSN: 1817-3195

# INDIRECT SLIDING MODE CONTROL OF A PERMANENT MAGNET SYNCHRONOUS MACHINE: FPGA-BASED IMPLEMENTATION WITH MATLAB & SIMULINK SIMULATION

#### <sup>12</sup>BADRE BOSSOUFI, <sup>1</sup>MOHAMMED KARIM, <sup>2</sup>SILVIU IONITA, <sup>3</sup>AHMED LAGRIOUI, <sup>3</sup> HASSAN MAHMOUDI

1) Laboratory of Data processing, Imagery and Analysis Numerical

Faculty of Sciences Dhar El Mahraz Fez, Morocco

2) Center of Modeling and simulation of the systems, Faculty of Electronics, Communications

University of PITESTI, Romania

3) Laboratory of Electrotechnics and Power Electronics Mohammadia School of Engineering

E-mail: <u>Badre\_isai@hotmail.com, karim\_lessi@yahoo.fr, silviu.ionita@upit.ro, lagrioui71@gmail.com, mahmoudi@emi.ac.ma</u>

#### **ABSTRACT**

These last thirty years were outstanding by the revolution of technology possibilities in the field of digital electronics and this, as much as within context of programmable solutions like (Microcontroller, DSP,...etc), than of reconfigurable solutions (CPLD, FPGA). Among all these possibilities, Field Programmable Gate Array (FPGA devises) is a good compromise between the advantage of the flexibility of a configurability solution, high frequency and the efficiency of a particular architecture with a high integration density.

In this paper is presents a detailed description of the structure by Indirect Sliding Mode of Permanent Magnet Synchronous Machine *PMSM*. Experimental results carried from a prototyping platform are given to illustrate the efficiency and the benefits of the proposed approach and the various stages of implementation of this structure in *FPGA*.

**Keywords:** FPGA, Indirect Sliding Mode Control, Permanent Magnet Synchronous Machine (PMSM), Power System Control, Systems Generator, Reusability, PWM.

#### 1. INTRODUCTION

The speed performance of new components and inherent flexibility of all programmable solutions give today many opportunities in the field of digital implementation for control systems [1]. This is especially available with software solutions implemented on general microprocessor or *DSP* [2]. However, specific hardware technology such as *FPGA* can also be considered as an appropriate solution in order to boost performances of controllers. These generic components combine low cost development, from their re-configurability with their specific software tools and more significant integration density.

The interest of *FPGA* technology is growing by increasing the number of designers in various application fields such as telecommunication, video, signal processing, embedded control

systems, and electrical control systems, the interest domain on this paper. Have already been the components used with success in many different applications such as Pulse Width Modulation (*PWM*), control of induction machine drives and multimachine system control. This is because the *FPGA*-based implementation of controllers can act efficiently and future challenges of this field [3].

With technological advance, the establishments of numerical nature became most widespread. The principal advantages of the numerical solutions are as follows:

- High flexibility of changing structures of control:

- Immunity against disturbances:

- No problems of parameters control variations.

With technological advancement, increased integration of FPGA devices is increasing.

#### **Journal of Theoretical and Applied Information Technology**

15<sup>th</sup> July 2011. Vol. 29 No.1

© 2005 - 2011 JATIT & LLS. All rights reserved

ISSN: 1992-8645 <u>www.jatit.org</u> E-ISSN: 1817-3195

Nowadays, the density of *FPGA* components can achieve the equivalent of *10* million logic gates with switching frequencies of around *500 MHz*. This allows the implementation of complex algorithms control in their entirety with a small period of time to load.

The inherent parallelism of *FPGA* components offers the possibility to run several algorithms in parallel control and configure them according to the defined criteria. Dynamic configuration between the algorithms control has as objective to select the appropriate algorithms depending on your point of operation. It may be useful also to ensure continuous operation in case of faults (sensors, switches ...).

In this paper, a new contribution for the *FPGA-Based* implementation of controls electrical. This approach is based on concept modularity and reusability.

This paper presents the realization of a platform for *Sliding Mode* control (*SMC*) of *PMSM* using *FPGA* based controller. This realization is especially aimed for future high performance applications. In this approach, not only the architecture corresponding to the control algorithm is studied, but also architecture and the *ADC* interface and *RS232 UART* architecture.

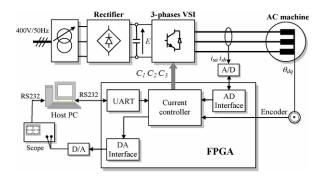

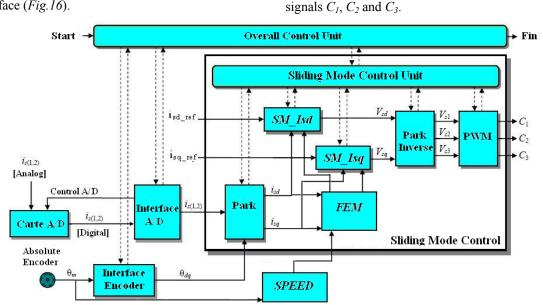

Considering the complexity of the diversity of the electric control devices of the machines, it is difficult to define with universal manner a general structure for such systems. However, by having a reflexion compared to the elements most commonly encountered in these systems, it is possible to define a general structure of an electric control device of machines which is show in *Fig. 1*:

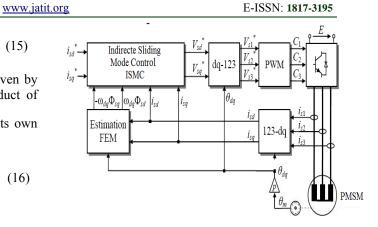

Fig.1: Architecture Control for PMSM

# 2. PRINCIPLE OF VARIABLE STRUCTURE SYSTEMS

The principle of variable structure systems has been studied primarily in the Soviet Union. Subsequently, much research on power systems control field has been made elsewhere to complement the theoretical study and find some possible applications. The sliding mode control is a particular operating mode of variable structure system. Using this command has been limited longer due to oscillations to the phenomena of slip and limitations of the switching frequency of power switches.

There are different regulatory structures by sliding mode current in systems based on variable structure sliding mode control.

Consider the following controlled system (1):

$$\frac{dy}{dt} = h(x) + G(x)u\tag{1}$$

Where u is the input vector of dimension, m, y is the state function of dimension, n, h is the state function describing the system evolution over time and G is a matrix of dimension n\*m. For the synthesis of a regulatory structure by sliding mode, it is necessary to define initially the switching function S(y) of dimension m.  $S(y) = \left[S_1(y)....S_m(y)\right]^r$ , where Si(y) is the i<sup>th</sup> switching function S(y).

The motor considered in this paper is an interior PMSM which consists of a 3 phase stator and a magnet rotor. The equations in:

$$u_{sd} = r_s \cdot i_{sd} + \frac{d\Phi_{sd}}{dt} - \omega \cdot \Phi_{sq}$$

(2)

$$u_{sq} = r_s \, i_{sq} + \frac{d\Phi_{sq}}{dt} - \omega \cdot \Phi_{sd} \tag{3}$$

$$\Phi_{sd} = L_d \cdot i_{sd} + \Phi_f \tag{4}$$

$$\Phi_{sq} = L_q.i_{sq} \tag{5}$$

$$Ce = \frac{3}{2} p \left[ \phi_f I_q + (L_d - L_q) I_d I_q \right]$$

(6)

$$Ce - C_r = J \cdot \frac{d\Omega}{dt} + f \cdot \Omega$$

(7)

Where  $\Omega$  is the rotation's speed, P the Number of pairs of poles, J the moment of inertia, f the Coefficient of viscous friction,  $C_r$  the Resistive torque,  $\Phi_f$  the flux produced by the permanent magnet,  $L_d$  and  $L_q$  the d-q axis stator inductance,  $r_s$  the stator winding resistance and  $C_e$  the electromagnetic torque.

#### **Journal of Theoretical and Applied Information Technology**

15<sup>th</sup> July 2011. Vol. 29 No.1

© 2005 - 2011 JATIT & LLS. All rights reserved

www.jatit.org

E-ISSN: 1817-3195

# 3. THE CONTROL LAW BASED ON SLIDING MODE CONTROL OF THE INVERTER DEVELOPMENT [5].

The control law sliding mode must simultaneously satisfy the conditions of invariance and attractiveness. To do this the switching function S(y) must satisfies:

• The invariance condition:

$$\begin{cases} S(y) = 0 \\ S(y) = 0 \end{cases}$$

(8)

• The attractiveness condition:

ISSN: 1992-8645

$$\begin{cases} \dot{S}_{i}(y) < 0 & si \quad S_{i}(y) > 0 \\ \dot{S}_{i}(y) > 0 & si \quad S_{i}(y) < 0 \end{cases}$$

for  $(i = 0...m)$  (9)

These conditions lead to determining a new vector control:

$$u^* = u_{eq} + u_{att} \tag{10}$$

The vector control given by equation (10) comprises two terms [7]:

The first is the control vector specifying the equivalent control for the system to stay on the sliding surface.

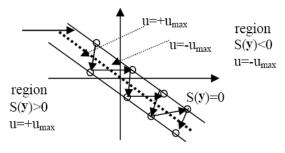

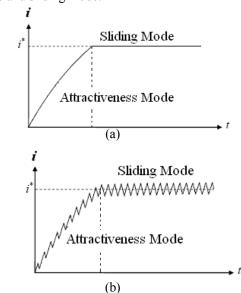

The second is the vector control that ensures the attractive control system outside the sliding surface. It also requires the system dynamics starting from an initial point until it reaches the sliding surface (Fig. 2) [9].

Fig.2: The state of Sliding Mode trajectory

# 4. INDIRECT CONTROL BY PMSM SLIDING MODE STATOR CURRENT

# 4.1. Synthesis of a-indirect control by sliding mode

The indirect control by sliding mode stator current vector of a permanent magnet synchronous machine ensures the calculation of direct and inverse components of the reference voltage vector expressed in the d-q plane. These components are

then applied across the phases of the stator *PMSM* through an intermediate stage of the *PWM*. The development of such law control must satisfy simultaneously the conditions of invariance and attractiveness given by equations (8) and (9). The terms  $-\omega_{dq}\Phi_{sq}$  and  $\omega_{dq}\Phi_{sd}$  are considered as terms of electromotive forces induced on the axis d and q and the expressions of the derivatives of the

switching function  $S_{isd}$  and  $S_{isq}$  are given by equations (11) and (12). Thus, the indirect control by sliding mode d and q components of stator current can be carried out by taking on each axis d and q. Therefore, each component  $V_{sd}^*$  and  $V_{sq}^*$  is composed by two terms as shown in equation (10). The first term is the equivalent voltage vector which is active in steady state, while the second term is the voltage vector which is attractive assets in transition.

$$\begin{cases} V_{sd}^* = V_{sdeq} + V_{sdatt} \\ V_{sq}^* = V_{sqeq} + V_{sqatt} \end{cases}$$

(11)

For trajectories currents  $i_{sd}$  and  $i_{sq}$  remained on their sliding surfaces ( $S_{isd}=0$  and  $S_{isq}=0$ ), apply the voltage vectors  $V_{sdeq}$  and  $V_{sqeq}$  on the axis d and axis q. These vectors can be calculated taking into account the following invariance conditions:

$$\begin{cases} S_{isd} = (i_{sd}^* - i_{sd}) = 0 \\ S_{isd} = 0 \end{cases} \Rightarrow \begin{cases} S_{isd} = i_{sd} \\ \frac{S_{isd}}{dt} = -\frac{1}{L_d} (V_{sdeq} - r_s i_{sd} + \omega_{dq} \Phi_{sq}) = 0 \end{cases}$$

$$\Rightarrow V_{sdeq} = r_s i_{sd} - \omega_{dq} \Phi_{sq} = r_s i_{sd}^* - \omega_{dq} \Phi_{sq} \qquad (12)$$

$$\begin{cases} S_{isq} = (i_{sq}^* - i_{sq}) = 0 \\ \dot{S}_{isq} = 0 \end{cases} \Rightarrow \begin{cases} i_{sq}^* = i_{sq} \\ \frac{S_{isq}}{dt} = -\frac{1}{L_q} (V_{sqeq} - r_s i_{sq} - \omega_{dq} \Phi_{sd}) = 0 \\ \Rightarrow V_{sqeq} = r_s i_{sq} + \omega_{dq} \Phi_{sd} = r_s i_{sq}^* + \omega_{dq} \Phi_{sd} \end{cases}$$

(13)

Considering the derived of switching functions and the control formulas, the new components  $V_{sd}^*$  and  $V_{sq}^*$  will be:

$$\begin{cases} V_{sd}^* = r_s i_{sd}^* - \omega_{dq} \Phi_{sq} - L_d \frac{S_{isd}}{dt} = V_{sdeq} + V_{sdatt} \\ V_{sq}^* = r_s i_{sq}^* + \omega_{dq} \Phi_{sd} - L_q \frac{S_{isq}}{dt} = V_{sqeq} + V_{sqatt} \end{cases}$$

(14)

From this attractive voltage vector system of reference voltage vector involves the switching

function derivative  $S_{isd}$  and  $S_{isq}$ . A structure of attractiveness is chosen at a constant speed and proportional action, which gives:

#### **Journal of Theoretical and Applied Information Technology**

15<sup>th</sup> July 2011. Vol. 29 No.1

© 2005 - 2011 JATIT & LLS. All rights reserved

$\begin{cases} V_{sdatt} = L_d (A_d \operatorname{sgn}(S_{isd}) + K_d S_{isd}) \\ V_{saatt} = Lq (A_a \operatorname{sgn}(S_{isa}) + K_a S_{isa}) \end{cases}$ (15)

By applying the reference voltage vector given by the previous system, the result of the product of

each of switching functions  $S_{isd}$  and  $S_{isq}$  its own derivative is given by the following system:

$$\begin{cases} S_{isd} \dot{S}_{isd} = -\frac{r_s}{L_d} S_{isd}^2 - A_d S_{isd} \operatorname{sgn}(S_{isd}) - K_d S_{isd}^2 \\ S_{isq} \dot{S}_{isq} = -\frac{r_s}{L_q} S_{isq}^2 - A_q S_{isq} \operatorname{sgn}(S_{isq}) - K_q S_{isq}^2 \end{cases}$$

(16)

In summary:

ISSN: 1992-8645

$$\begin{bmatrix} V_{sd}^* \\ V_{sq}^* \end{bmatrix} = r_s \begin{bmatrix} i_{sd}^* \\ i_{sq}^* \end{bmatrix} + \begin{bmatrix} -\omega_{dq} \Phi_{sq} \\ \omega_{dq} \Phi_{sd} \end{bmatrix} + \begin{bmatrix} L_d & 0 \\ 0 & L_q \end{bmatrix}$$

$$\begin{pmatrix} A_d & 0 \\ 0 & A_q \end{bmatrix} \begin{bmatrix} \operatorname{sgn}(S_{isd}) \\ \operatorname{sgn}(S_{isq}) \end{bmatrix} + \begin{bmatrix} K_d & 0 \\ 0 & K_q \end{bmatrix} \begin{bmatrix} S_{isd} \\ S_{isq} \end{bmatrix}$$

(17)

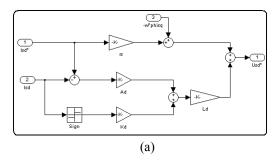

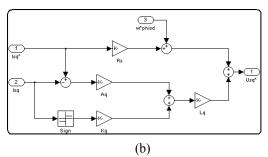

The following figure shows the sliding mode correction block diagram, satisfying the attractiveness and invariance conditions:

Fig. 3: Block diagram of the corrector indirect sliding Mode (a) isd, (b) isq.

Fig. 4: Indirect Sliding Mode Control applied to a PMSM

For a given value of the reference current, the current i trajectory described by the system from *Fig.3* is shown in *Fig.5*. The trajectory obtained is characterized by two stages: the attractiveness mode and sliding mode.

Fig.5: Trajectory characterizing the indirect control mode by sliding (a) Continuous operation (b) Discrete operation

From this entire process, systems with variable structure controlled by an indirect sliding mode control have several properties:

The system doesn't dependent only on the sign of the switching function, but also it depends on its value.

The dynamics of the system controlled by such control depends essentially on the coefficients choice of the attraction mode matrices K and A.

The theory of indirect sliding mode is appropriate to systems whose control is discontinuous.

#### Journal of Theoretical and Applied Information Technology

15<sup>th</sup> July 2011. Vol. 29 No.1

© 2005 - 2011 JATIT & LLS. All rights reservedwww.jatit.org

E-ISSN: 1817-3195

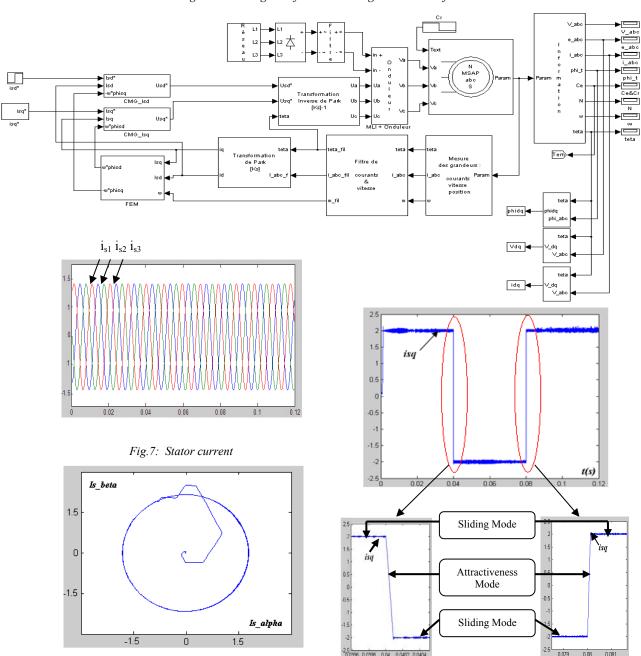

#### 4.2. Results of simulations

ISSN: 1992-8645

The Fig. 6 shows the general structure of sliding mode control of the PMSM stator current in the dq reference. The  $i_{sd}$  and  $i_{sq}$  currents are subjected to the transformation of Concordia for components  $i_{s\alpha}$  and  $i_{s\beta}$ . Each component is controlled by a sliding mode corrector that provide the reference  $U_{sd}^*$  and  $U_{sq}^*$  dependant by the

electromotive forces of voltages. The result is applied to the Pulse Width Modulation (PWM) component used for controlling the voltage inverter, which generates three-phase voltages  $V_a$ ,  $V_b$  and  $V_c$  that are subject to a Park transformation. Finally, the  $V_{sd}$  and  $V_{sq}$  are applied directly in PMSM.

Fig. 6: Block diagram of indirect sliding mode control for PMSM

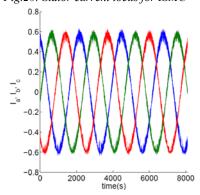

Fig.8: Instead of the current vector in the plane  $(\alpha, \beta)$

Fig.9: Quadratic Current isa

#### **Journal of Theoretical and Applied Information Technology**

15<sup>th</sup> July 2011. Vol. 29 No.1

© 2005 - 2011 JATIT & LLS. All rights reserved

E-ISSN: 1817-3195

Fig.10: Voltage V<sub>s1</sub>

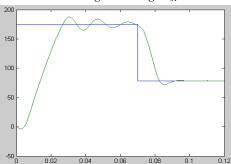

Fig.11: Speed Rotor

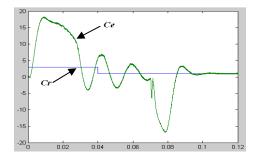

Fig.12: Torque electromagnetic

In the Fig. 7 to 12 are show the simulation result of indirect control by sliding mode stator when the current is applied between  $+I_{sn}$  and  $-I_{sn}$  (E=380V, frequency PWM=5 KHz,  $K_d=K_q=A_d=A_q=320$ ). It should be noted that the dynamics of the transient is lower than that obtained with other commands. However, the current has better quality control in steady state with fewer oscillations.

The choice of coefficients  $A_d$ ,  $A_q$ ,  $K_d$  and  $K_q$  was selected by follows criteria:

- The module reference voltage vector must not exceed the maximum amplitude that can generate voltage of the inverter.

- Coefficients chosen provide good robustness against parameter variations where the higher coefficients provide better control.

The coefficients should not cause strong current oscillations.

The chosen coefficients are the result of several simulations where the selection criteria is it a good factor.

These coefficients allow controlled quantities to follow their references to an error of about 99% on the PMSM parameters ( $L_d$ ,  $L_q$  and  $r_s$ ).

# 5. DEVELOPMENT OF THE DESIGN METHODOLOGY

#### 5.1. FPGA devises

There are several manufacturers of FPGA Actel, Xilinx components such: Altera...etc. These manufacturers use different technologies for the implementation FPGAs. These technologies attractive are because they provide reconfigurable structure that is the most interesting because they allow great flexibility in design.

Nowadays, *FPGAs* offer the possibility to use dedicated blocks such as *RAMs*, multipliers wired interfaces *PCI* and *CPU* cores.

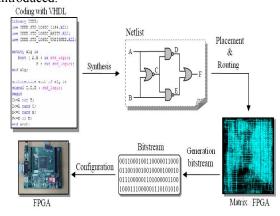

The architecture designing was done using with CAD tools. The description is made graphically or via a hardware description language high level, also called HDL (Hardware Description Language). Is commonly used language VHDL and Verilog. These two languages are standardized and provide the description with different levels, and especially the advantage of being portable and compatible with all *FPGA* technologies previously introduced.

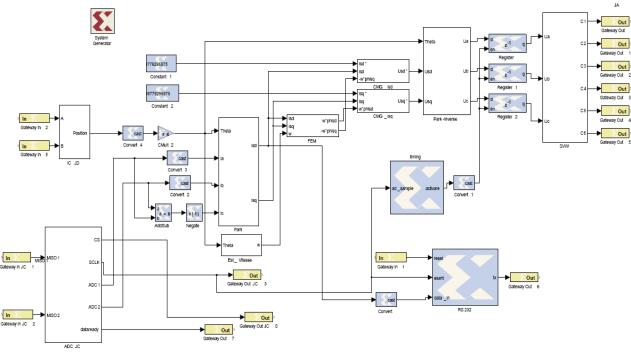

Fig.13: Functional Model DTC from SYSTEM GENERATOR

The Fig. 13 summarizes the different steps of programming an FPGA. The synthesizer generated with CAD tools first one Netlist which

#### Journal of Theoretical and Applied Information Technology

15<sup>th</sup> July 2011. Vol. 29 No.1

© 2005 - 2011 JATIT & LLS. All rights reserved

www.jatit.org

E-ISSN: 1817-3195

describes the connectivity of the architecture. Then the placement-routing optimally place components and performs all the routing between different logic. These two steps are used to generate a configuration file to be downloaded into the memory of the *FPGA*. This file is called bitstream. It can be directly loaded into *FPGA* from a host computer.

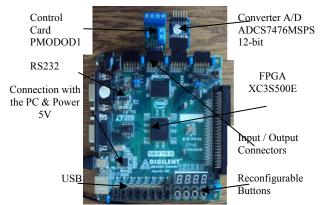

In this paper an *FPGA XC3S500E* Spartan3E from *Xilinx* is used. This *FPGA* contains 400,000 logic gates and includes an internal oscillator which issuer a 50MHz frequency clock. The map is composed from a matrix of 5376 slices linked together by programmable connections (*Fig.14*).

Fig. 14: The FPGA XC3S500E Sparian

#### 5.2. Simulation Procedure

ISSN: 1992-8645

The simulation procedures begin by checking the control algorithm functionality trough a functional model using Simulink (System Generator for Xilinx) blocks. For this application, the functional model consists in a Simulink model of the Indirect Sliding mode Control algorithm associated with a voltage inverter and *PMSM* model. *Fig.* 15 gives a global view of the functional model.

Fig.15: The Schematic Bloc of Functional Model

The description of the different modules is detailed below:

- The blocks of coordinate's transformation: the transformation of Park Inverse (abc-todq);

- The blocks of coordinate's transformation: the transformation of Park (*dq-to-abc*);

- The *PWM* block is the most important, because can provide control pulses to the *IGBT* voltage inverter in the power section from well-regulated voltages;

- Two blocks Sliding Mode Corrector for the regulation of currents  $I_{sd}$  and  $I_{sq}$  from the

#### **Journal of Theoretical and Applied Information Technology**

15<sup>th</sup> July 2011. Vol. 29 No.1

© 2005 - 2011 JATIT & LLS. All rights reservedwww.jatit.org

E-ISSN: 1817-3195

comparison of measured values and reference values of stator currents;

ISSN: 1992-8645

- The block for FEM calculation and speed estimator:

- The block encoder interface IC allows the adaptation between the FPGA and the acquisition board to iniquity the rotor position of the PMSM;

- The ADC interface allows the connection between the FPGA and the analog-digital converter (ADCS7476MSPS 12-bit A / D) that interfaces two Hall Effect transducers for the stator currents machine acquisition;

- Block "Timing" which controls the synchronization between blocks, which allows the refresh in the voltages reference V<sub>10</sub>, V<sub>20</sub> and V<sub>30</sub> at the beginning of each sampling period;

- The RS232 block provide the signal timing and recovery of signals viewed, created by another program on Matlab & Simulink to visualize the desired output signal.

#### 6. EXPERIMENTAL SET-UP

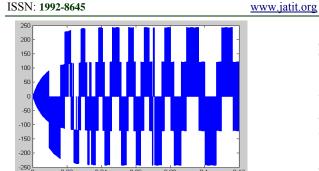

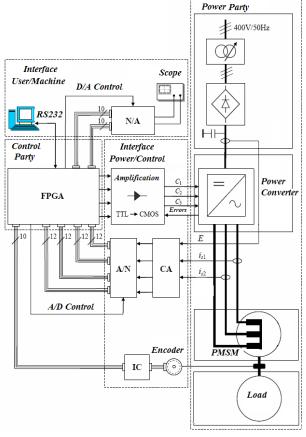

To implementing the control system by Sliding mode Control is it used a *XC3S500E Spartan3E*, *ADC* (analog to digital convertor) interface (*Fig.16*).

The control unit architecture ensures a control module for an A/D interface, an encoder interface and the control Sliding module. The A/D interface module and encoder interface are activated simultaneously at the beginning of each sampling period. Then, after a delay conversion from analog to digital conversion  $t_{ADC}$ , the control unit activates the control module indirect sliding mode. This module is controlled by its own control unit. First times, the Park transformation module will calculate the components of  $i_{sd}$  and  $i_{sq}$  ( $t_{abc-dq}$ ). Then, when the processing module abc-dq indicates the end of its calculation, the estimation module of the FEM is activated, has to calculate  $-\omega_{dq}\Phi_{sa}$ and  $\omega_{da}\Phi_{sd}$  . It is running for  $t_{FEM}$  time. Then the  $SM\_I_{sd}$  and  $SM\_I_{sq}$  modules are enabled computing in parallel the tensions  $U_{sd}^*$  and  $U_{sq}^*$  $(t_{SM\ da})$ . Thereafter, when the modules indicate the end of the calculation, inverse Park transformation module is activated and calculates the reference voltages  $U_{sa}^*$ ,  $U_{sb}^*$  and  $U_{sc}^*$  ( $t_{qd-abc}$ ). After the PWM module is enabled. Latter has a computational time equal to  $t_{PWM}$  and can calculate and refresh the reference voltages  $V_{10}$ ,  $V_{20}$  and  $V_{30}$  which will be compared to a triangular carrier signals that generate control

Fig.16: FPGA Based Hardware ISMC

The following table shows the performance of computing time and resource consumption, obtained during the control Sliding Mode architecture implementation. The resources consumed are obtained for a fixed point format

13/Q12. The total computing time  $t_{SMI}$ , in command module is equal to  $1.04\mu s$ . By adding the analog to digital conversion time  $t_{A/D}$ , total time Tex architecture brought dives equals  $3.48\mu s$ .

#### Journal of Theoretical and Applied Information Technology

15<sup>th</sup> July 2011. Vol. 29 No.1

© 2005 - 2011 JATIT & LLS. All rights reservedwww.jatit.org

E-ISSN: 1817-3195

| Module                                                                                        | Latency           | Time                              |

|-----------------------------------------------------------------------------------------------|-------------------|-----------------------------------|

|                                                                                               |                   | Calculation                       |

| Interface A/D                                                                                 | 120               | t <sub>A/D</sub> =2.4 μs          |

| IC Interface                                                                                  | 2                 | t <sub>Cod</sub> =0.04 μs         |

| Park                                                                                          | 16                | t <sub>abc-dq</sub> =0.30 μs      |

| FEM                                                                                           | 15                | $t_{\rm C} = 0.24 \; \mu {\rm s}$ |

| SM_I <sub>sd</sub>                                                                            | 8                 | $t_{SM_{dq}} = 0.75 \ \mu s$      |

| Park-Inverse                                                                                  | 14                | tdq -abc=0.30 μs                  |

| SM_I <sub>sq</sub>                                                                            | 18                | $t_{SM_{dq}} = 0.75 \ \mu s$      |

| PWM                                                                                           | 5                 | t <sub>PWM</sub> =0.014μs         |

| $t_{\text{SMI}} = t_{\text{abc-dq}} + 2t_{\text{SM dq}} + t_{\text{dq-abc}} + t_{\text{PWM}}$ |                   | $t_{FOC} = 1.04  \mu s$           |

| Run time $T_{ex} = T_{A/D} + t_{SMI}$                                                         |                   | $t_{\rm ex} = 3.48 \ \mu s$       |

| Resources                                                                                     | Number of Slices  | 1344 de 5376 (25%)                |

| Consumed                                                                                      | Wired Multipliers | 8de 16 (65%)                      |

|                                                                                               | Memory RAM        | 7%                                |

ISSN: 1992-8645

Table1: FPGA Performance for ISMC

To test the controller, a prototyping platform for a Permanent magnet Synchronous Machine was assembled..

Fig.17: Experimental setup of the testbed

Fig.18: Prototyping platform control

The Fig.17 and Fig.18 shows the experimental results obtained during the implementation of the Sliding Mode indirect control. It presents the control signals state for the switches of the inverter voltage in the area where there is the reference voltage vector. These results are similar to those presented in the theories. Furthermore, the control signals generated from the FPGA board will be filtered before being injected into the voltage inverter.

The above figures show that the phases are balanced and demonstrate the proper functioning of the *PWM*.

#### Journal of Theoretical and Applied Information Technology

15<sup>th</sup> July 2011. Vol. 29 No.1

© 2005 - 2011 JATIT & LLS. All rights reserved

ISSN: 1992-8645 <u>www.jatit.org</u> E-ISSN: 1817-3195

Fig. 19: Switching states of control signals  $C_1$  and  $C_2$  The Fig. 19 shows that control system satisfy the basic requirements of the control strategy and validate therefore the good functionality of the system. In fact, It can be noted that:

- The switching frequency is limited to the sampling frequency of the control algorithm to guarantee safe operation of the semiconductor power devices.

- The switching frequency increases weakly when the stator current vector magnitude decreases.

The indirect sliding mode control is synthesized using the sliding mode theory. In this case, a reference voltage vector is applied to the machine. This voltage vector is composed by a vector voltage equivalent valid on the sliding surface and a vector attraction voltage valid outside the sliding surface (transient). The application of the vector reference voltage to *PMSM* requires an intermediate stage of pulse width modulation. The switching frequency is fixed equal to the frequency of the *PWM*.

The indirect control by sliding mode ensures better quality control currents in steady state with a considerable reduction of the oscillations.

The implementation of the indirect control by sliding mode on *FPGA* devices is characterized by a reduced operation time.

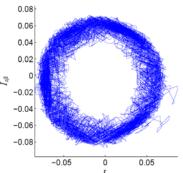

Fig.20: Stator current locus for ISMC

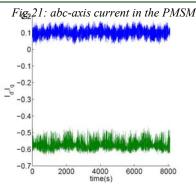

Fig. 22: d-axis and q-axis current in the PMSM

In figures 20, 21 and 22 the experimental results of Indirect Sliding Mode PMSM with the FPGA platform are shown. Update frequency for this implementation is 20kHz. All results were extracted from the FPGA by the ChipScope tool of Xilinx.

#### CONCLUSION

In the case of a Sliding mode controlled by current stator of permanent magnet synchronous machine, it is required the use of the PWM technique. This paper presents implementation of Sliding Mode Control architecture on FPGA for Permanent Magnet Synchronous Machine (PMSM). development of the corresponding design has rigorously followed an appropriate methodology which offers considerable advantages and allows the creation of a library for optimized reusable modules.

Among the advantages of this control structures, the switching frequency is fixed and there is compliance with the eight vector voltages that can provide the voltage inverter. However, it has disadvantages because the general structure of the control algorithm is complex to implement and parameters of the control algorithm depend on the sampling period.

#### ACKNOWLEDGEMENTS

We thank all those who contributed to make this work, including my teachers in the *Center of Modeling and simulation of the systems*, University of Pitesti from Romania and in my home laboratory LIIAN from Morocco, and all my friends for their support.

#### Journal of Theoretical and Applied Information Technology

15<sup>th</sup> July 2011. Vol. 29 No.1

© 2005 - 2011 JATIT & LLS. All rights reservedwww.jatit.org

E-ISSN: 1817-3195

# ISSN: 1992-8645 REFERENCES:

- [1] Y.Y. Tzou, H.J. Hsu: "FPGA Realization of Space-Vector PWM Control IC for Three Phase PWM Inverters," *IEEE Trans, Power Electron.*, vol.12, n°6, pp.953-963, nov.1997.

- [2] E. MONMASSON, and M. Cirstea "FPGA Design Methodology for Industrial Control Systems – A Review," *IEEE Trans Ind. Electron..*, vol.54, no. 4, pp.1824-1842, August. 2007.

- [3] Y. Kebbati, Y.A. Chapuis and F. Braun, "Reuse methodology in FPGA/ASIC Digital Integration Solution for Vector Control of Motor Drives", in Proceeding of IEEE International Symposium on Signal, Circuit and Systems (SCS'2001), PP.333-33-, Romania, 2001.

- [4] X. Lin-Shi, F. Morel, A. M. Llor, B. Allard and J.M. Retif "Implementation of Hybrid Control for Motor Drives," *IEEE Trans. Ind Electron.*, vol.54, no.4, pp.19446-1952, August. 2007.

- [5] H. T. moon, H. S. Kim and M. J. Youn, "A Discret Time Predictive Current Control for PMSM" *IEEE Trans. Power Electronic.*, vol.18, no.1, pp. 464-472, Janvier. 2003.

- [6] H.J. Lee; S.K. Kim; Y.A. Kwon; S.J. Kim, "ASIC design for DTC based speed control of Induction motor," in Proc. IEEE ISIE'01 Conf., 2001, pp. 956 –961

- [7] M.W. NAOUAR, « Commande numérique à base de composants FPGA d'une machine synchrone », algorithmes de contrôle du courant, *Thèse de Doctorat*, Ecole Nationale d'Ingénieurs de Tunis et l'Université de Cergy Pontoise, Tunis, 2007.

- [8] E. Monmasson; B. Robyns; E. Mendes, B. De Fornel, "Dynamic reconfiguration of control and estimation algorithms for induction motor drives," *in Proc. IEEE ISIE Conf.*, 2002, pp. 828 –833.

- [9] A.Lagrioui; H.Mahmoudi; "Current and Speed Control for the PMSM Using a Sliding Mode Control" 2010 IEEE 16th International Symposium for Design and Technology in Electronic Packaging (SIITME), Pitesti, Romania.

- [10] G.R. Walker, "Digitally-Implemented naturally sampled PWM suitable for multilevel converter control, "IEEE Trans. Ind. Electron., vol. 18, n°6, pp. 1322-1329, Nov.2003.

- [11] Xilinx Data Book, 2006, available; www.xilinx.com.