<u>30<sup>th</sup> November 2023. Vol.101. No 22</u> © 2023 Little Lion Scientific

ISSN: 1992-8645

www.jatit.org

E-ISSN: 1817-3195

# AN IMPROVED PROPORTIONAL RECONFIGURABLE INTEGRATED DECODING WITH BELIEF PROPAGATION (PRDBP) FOR 5G COMMUNICATIONS

## PECHETTI GIRISH<sup>1</sup>, BERNATIN T<sup>2</sup>

<sup>1</sup>Research Scholar, Department of ECE, Sathyabama Institute of Science and Technology

(Deemed to be University), Chennai - 600 119. Tamil Nadu, India

<sup>2</sup>Associate Professor, Department of ECE, Sathyabama Institute of Science and Technology (Deemed to be

University) Chennai - 600 119. Tamil Nadu, India

#### ABSTRACT

Recently, Fifth Generation (5G) communication network uses the Low-Density Parity Check (LPDC) codes due to minimized latency in the radio channel. The conventional LPDC uses the standard decoders that use an iterative message-passing (IMP) algorithm with iterative decoding based on belief propagation (IDBP) or the sum-product algorithm (SPA). Those iterative message algorithms are operated in a loopy graph with the maximum-likelihood estimation which leads to higher computation complexity for the dynamic update. To overcome the issues proportional reconfigurable decoding model is utilized in place of an iterative algorithm to perform low-density parity check (LDPC) decoding. Additionally, the 5G network demands for higher throughput, compatibility and minimal complexity. This paper proposed an Integrated Proportional Reconfigurable Decoding with Belief propagation (PRDBP) to increase the throughput in the 5G wireless communication channel. The proposed PRDBP model focused on linear error-correcting codes in 5G channels. The model computes the enumerator's code word length for the finite length of code ensembles. The PRDBP model considers the block-length computation for the asymptotic cases to compute the minimal sensing distance. The code ensemble in the PRDBP model characterized the trapping set, stopping set, and properties of the code word in minimal floors. The proposed PRDBP model integrates the sum products and belief propagation algorithm for the modification in node equations. Based on certain class interior point estimation method linear problem and nonlinear convex optimization problems are computed. Based on computation affine scaling, reduction method and path-following methods are implemented.

Keywords: Low Density Parity Check, Iterative Message-Passing, Proportional Reconfigurable Decoding, Fast Fourier Transformation, Progressive Edge Growth, Sum Product Algorithm.

#### 1. INTRODUCTION

space in the case of wireless Free communications or a pair of wires, coaxial cable, or optical Fiber in the case of wired communications [1]: a communication system acts as a medium for the transfer of mutual information. The transmitter, the transmission channel, and the receiver are just some of the components that make up a standard communication system. Error Control Coding (ECC) is rapidly becoming a requirement for the secure transmission and storage of massive volumes of data in wireless communication networks. For code speeds below the channel capacity [2], Shannon claims that ECC techniques are primarily used to recover the original data at the receiver by lowering the transmission errors (channel errors) to any desired value. Over the years, many research works have been carried out towards the development of efficient ECC schemes to increase the transmission rate, in hopes to reach the channel capacity as proposed by Shannon. In recent times, one of the most successful types of ECC scheme in doing so has been Low-Density Parity-Check (LDPC) codes [3]. Since their rediscovery in the late 1990's, LDPC codes are shown to exhibit performance close to the Shannon's limit for a wide range of channels [4].

Both the matrix form and the graphical form are useful representations of LDPC codes, which are a type of linear block codes. The sparse parity-check matrix H [5] is a useful tool for efficiently representing LDPC codes in matrix form. The sparseness of the non-zero components in the

<u>30<sup>th</sup> November 2023. Vol.101. No 22</u> © 2023 Little Lion Scientific

ISSN: 1992-8645www.jatit.orgparity-check matrix [6] is the only distinction<br/>between the LDPC code and any other block code.time<br/>conveSparse parity-check matrices, in which fewer<br/>entries are not zero, are commonly used to represent<br/>LDPC codes. The degree distribution [7] is the sum<br/>of the numbers of non-zero entries in each row and<br/>column of the parity-check matrix. Each row and<br/>column of the parity-check matrix contributes to the<br/>overall weight of the LDPC code based on the total<br/>amount of non-zero components present there.WWW.jatit.org

In electronic communication, Error Correcting Codes (ECC) is widely utilized for the effective storage design and error free data transmission in the desire bandwidth [8]. Low density parity check (LDPC) codes error correction is considered as the next generation for effective data transmission to reduce the data rate with the Shannon's limit. LPDC codes rediscover the decoding procedure for the correction for the minimization of error in channel through relative signal-to-noise ratio (SNR) for the significant reduction in complexity [9]. With the prior error correction and implementation of parallelism LDPC hardware is performed based on wireless communication with the DVB-S2 standard, Wi-MAX IEEE (802.16) (IEEE Std 802.16-2009) and WLAN IEEE (802.11n) [10]. Conventionally, LDPC decoding algorithm utilizes the conventional Sum Product algorithm (SPA) with the iterative passing of message to achieve the effective performance in decoding. The performance of SP algorithm exhibits effective bit error rate (BER) the utilization of logarithmic with and multiplicative computation in process for the loglikelihood (LLR) between the nodes in wireless communication [11]. The implementation of SPA exhibits the higher computational complexity those difficult for the implementation in hardware. To eliminate the conventional SPA complexity Simplified Sum-Product algorithm (SSPA) and Modified Sum-Product algorithm (MSPA) is adopted [12]. The SPA model simplifies and modify the non-linear function-based quantization approximation region division. However, the SPA method significantly minimizes the computational complexity leads to degradation of wireless communication performance [13]. LPDC codes with the SPA model utilizes simple hard decision to reduce the complexity in decoding algorithm for the implementation of complexity reduction compared with the conventional SPA. Recently, LDPC decoding lattices comprises of Fast Fourier transform based Sum-Product algorithm for the reduction of computational complexity [14]. However, with the conventional SPA model implementation of FFT increases the computation

atit.orgE-ISSN: 1817-3195time in implementation. Furthermore, the<br/>conventional FFT is difficult for processing larger<br/>dataset for the larger bandwidth.

This paper proposed an Integrated Proportional Reconfigurable Decoding with Belief propagation (PRDBP) to increase the throughput in the 5G wireless communication channel. The proposed PRDBP model focused on linear error-correcting codes in 5G channels. The model computes the enumerator's code word length for the finite length of code ensembles. The PRDBP model considers the block-length computation for the asymptotic cases to compute the minimal sensing distance. The code ensemble in the PRDBP model characterized the trapping set, stopping set, and properties of the code word in minimal floors. The proposed PRDBP model integrates the sum products and belief propagation algorithm for the modification in node equations. Based on certain class interior point estimation method linear problem and nonlinear convex optimization problems are computed. Based on computation affine scaling, reduction method and path-following methods are implemented.

# 2. RELATED WORKS

The conventional papers which presented decoding techniques for LDPC codes are considered. Some related works have been studied those accounts for highly efficient decoding schemes as well as its VLSI implementation in hardware that are in proximity to our proposed methodology.

Using RS-LDPC codes with a random parity check matrix, [15] looked into various implementation strategies for the BC. Reed-Solomon based low-density parity-check (RS-LDPC) codes are the building blocks of the new **RS-LDPC** architecture. The **BC-RSLDPC** architecture comprises of decoder and switch with implementation of parity check implemented with the higher efficiency techniques. The developed model achieves the decoder rate value of 1.3M gates of operating frequency value of 450MHz with throughput value of 41Gbps based on consideration of 8 iterations.

In [16], we reported a log-likelihood-ratio based belief-propagation (LLRBP) decoding of LDPC codes and its simplified variants. Both a normalization term and an additive offset term can be incorporated into the BP-based approximation to simplify check node updates. They found that both offset and normalized BP-based decoding methods performed similarly to BP decoding while offering advantages for hardware implementation. These

<u>30<sup>th</sup> November 2023. Vol.101. No 22</u> © 2023 Little Lion Scientific

ISSN: 1992-8645

www.jatit.org

E-ISSN: 1817-3195

LDPC codes were decoded through belief propagation of the parity check matrix under factor graph representation, which was first analyzed in [17] and hence referred to as 'Tanner graph'. The Sum Product Algorithm (SPA) is defined as a message passing algorithm over a factor graph and it is described in [18]. They demonstrated the implementation of BCJR algorithm, Pearl's belief propagation and Turbo decoding as instances of the sum-product algorithm. The algorithm corrected all bursts of length 11 or less and the weight six error patterns tested were decoded in five or fewer iterations. In [19] proposed a GF (64)-LDPC decoder integrated with the Min-Sum algorithm for the minimal code rate and length value of less than 0.7dB for the varying code rate with the Belief Propagation algorithm.

Their strategy can be modified to effectively interpret Galois Fields of orders GF (4096) and higher. Trial results demonstrated that the decoder region of a Virtex 4 FPGA requires less than 20% of the device's resources to achieve a translating throughput of 2.95Mbps.In [20] planned a LDPC decoder utilizing wave pipelining idea, which decreases the degree of idleness of the unravelling system. This study gave the definite interior engineering and its plan intricacy as far as equipment usage factors. Their combination report showed that the wave pipelined design lessens the region above and idleness above.

By shortening the quantization word length of unraveling data, [21] established the idea of memory-effective LDPC decoder, which in turn restricted the complexity of the required hardware. Using a short word length and a guaranteed cycle mistake rate (BER), two quantization methods were developed to lessen the number of memory bits anticipated by the decoder setup. The results demonstrated that the two quantization schemes reduced equipment complexity with minimal impact on decoding efficiency.In [22] a calculation that was near WBF family calculations in intricacy was introduced. The calculation is called as Liu-Pados Weighted Piece Flipping (LP-WBF), and known to perform well particularly for limited math LDPC codes. This calculation utilized the most undependable and the most solid variable piece in an equality really take a look at condition to compute the measurement. The calculation accomplished an engaging execution versus intricacy trade-off for limited math LDPC codes. Another BF calculation was introduced which is a self-unwavering qualitybased calculation. The measurement is processed from the quantity of fulfilled and unsatisfied equality really look at conditions, and the selfdependability upsides of the variable pieces. This calculation proceeded as well as MWBF and demonstrates the significance of the selfdependability in the flipping choice.

#### 3. PROPOSED METHODOLOGY 3.1 LDPC Code with PRDBP

(LDPC) Low-Density Parity-Check effective model for the performance of channel improvement with the Shannon capacity channel estimation model. LDPC codes are implemented for the effective practical implementation to achieve reliable data transmission to achieve Shannon capacity. The Shannon capacity of the channel code is estimated based on the code rate to achieve error number near to zero for the decoding with the maximum likelihood estimation-based decoder with increase in length of block. The developed PRDBP uses the random linear block codes with polynomial code. The increase in length of block performs error value as zero, this leads to the increased computation complexity for the encoding and decoding to increases throughput, speed and reduced area. The PRDBP model implemented with LDPC code considers the Shannon limit with the block length with additional advantages to minimize the complexity for the higher speed and accuracy.

Figure 1: Channel in LDPC

With proposed PRDBP model simplest coding is implemented with the utilization of single parity check code. The developed code utilizes the extra bit in the binary message transmission for the relied message bits. Through parity code additional message bits are implemented with XOR sum with the codeword of 0. LDPC codes are also stated as the error correcting code with the provision of channel capabilities based on the Shannon limit with consideration of features for the effective implementation. As the proposed PRDBP model uses the iterative belief propagation decoding process for the reduced complexity and area with the increase in throughput. The adoption of belief propagation decoding process PRDBP model minimizes the low design and cost for the hardware

| <u>30<sup>th</sup></u> | <sup>1</sup> <u>November 2023. Vol.101. No 2</u> | 2 |

|------------------------|--------------------------------------------------|---|

|                        | © 2023 Little Lion Scientific                    |   |

| ISSN: 1992-8645         | www.j                      | atit.org             |      | E-ISS    | SN: 1817-3195 |

|-------------------------|----------------------------|----------------------|------|----------|---------------|

| design The IDDC norfers | n tha inharant narallalism | variables estimation | Each | variable | a aammutad    |

design. The LDPC perform the inherent parallelism for the distributed mapping in parallel computation to achieve higher throughput and reduced latency. The communication model system comprises of different modules such as LDPC encoder, decoder and AWGN channel as illustrated in figure 1.

In general, for an n-bit codeword, the total number of possible combinations of a binary vector is 2n. This n-bit codeword comprises of k message bits and (n-k) redundant bits. The parity-check matrix H is then represented as in equation (1)

$$H = \begin{bmatrix} A, I_{n-k} \end{bmatrix}_{k \times n} \tag{1}$$

where,  $k \times n$  represents the size of the matrix H, having k rows and n columns,  $I_{n-k}$ represents identity matrix of order n-k and A is a  $k \times n$  binary matrix. Then, by performing Gauss-Jordan elimination on PCM H, a  $k \times n$ generator matrix G is obtained as in equation (2)

$$\boldsymbol{G} = \left[ \boldsymbol{I}_{k^{\prime}} \boldsymbol{A}^{T} \right]_{k \times n} \tag{2}$$

The encoding operation in the encoder and the parity-check operation in the decoder are given as in equation (3) and (4)

$$C_n = M_k \times G \tag{3}$$

$$P_k = C_n^r \times H^T \tag{4}$$

where, C is the codeword, M is

the message bits,  $C_n^r$  is the received codeword at the decoder and P is the parity-check bits. The syndrome of the received codeword is given as in equation (5)

$$S = C^r \cdot H^T \tag{5}$$

The parity check condition is satisfied if and only if  $C.H^T = 0$

LDPC Decoding with PRDBP

In general, the proposed PRDBP model uses the LDPC model for the transmission of message between node with the Shannon values. The message passing algorithm is lamented for the decoding process with the iterative process as presented in sequence of steps

Input: The probabilities of the code are represented  $p_n^0 = P(x_n = 0)$  and  $p_n^1 = P(x_n = 1) = 1 - p_{n,n}^0 = 1, \dots, N$ Output: Decision value for hard  $\hat{X} = \{\hat{x}_1, \dots, \hat{x}_N\}$

#### Step 1: Initialization

Initially, iterative based decoding process is implemented for the computation of priori probabilities estimation with the neighboring node

variables estimation. Each variable is computed based on computation of Log-Likelihood Ratio

(LLR)

$$\varphi_n$$

is computed as in equation (6)

$\varphi_n = \log \frac{p_r(p_n^0 = 0 | y_{\bar{i}})}{p_r(p_n^0 = 0 | y_{\bar{i}})} = \frac{2}{\pi} y_i$

$$\rho_n = \log \frac{1}{\rho_r (\rho_n^1 = 1 | y_{\bar{i}})} = \frac{1}{\sigma^2} y_i \tag{6}$$

where,  $\mathcal{Y}_i$  denotes output value in the channel and  $\sigma^2$  represented the channel noise variance.

For every

$$(c, V) \in \{(i, j) | H_{i,j} = 1\}$$

, compute as in equation (7)

$$B_{vc} = sign(\varphi_n) log \left[ \frac{1 + e^{-|\varphi_n|}}{1 - e^{-|\varphi_n|}} \right]$$

(7)

Where,

$$sign(\varphi_n) = \{+1 \text{ if } \varphi_n \ge 0 \text{ and} - 1 \text{ if } \varphi_n < 0\}$$

Based on the output channel the node variables are initiated with the iterative based decoding process.

#### **Step 2 : Iterative decoding process**

computation of posteriori In the probabilities estimation extrinsic messages are computed for the variable neighboring node computation. For every node c and variable v the computed as in equation (8)

$$\begin{aligned} \alpha_{cv} &= \log \left| \frac{1 + e^{\beta}}{1 - e^{-\beta}} \right| \prod_{n \in N(c)/v} sign(\beta_{vc}) \\ & \text{Where,} \quad \sum_{n \in N(c)/v} |\beta_{vc}| \quad \text{and} \quad \alpha_{v} \end{aligned}$$

estimated based on the LLR information node check c for the different variable node v.

Variable node processing: For every iteration the extrinsic messages are computed for the distant neighbors and initial decision process. For every node c and variable v computed as in equation (9)

$$\beta_{vc} = sign(\phi_{m,n}) \log \left| \frac{1 + e^{-|\phi_{m,n}|}}{1 - e^{-|\phi_{m,n}|}} \right| \tag{9}$$

$$Where \quad \phi_{m,n} = \phi_n + \sum_{n \in \mathcal{N}(\sigma) \setminus v} \alpha_{ev}$$

and  $\beta_{\rm wc}$  provides the variable node information for the node check c.

For every node variable v, the posteriori value is computed using the equation (10)

$$\gamma_n = \phi_n + \sum_{m \in \mathcal{M}(v)} \alpha_{vv} \tag{10}$$

Step 3: Decision

The process is terminated based on condition  $\hat{\mathbf{x}} \cdot \mathbf{H} = 0$ , initiated with the updated node check with estimation of parity check satisfied based on the decoding iteration fro the iteration number.

| ISSN: 1992-8645 | www.jatit.org | E-ISSN: 1817-3195 |

|-----------------|---------------|-------------------|

|                 |               |                   |

LDPC codes with their iterative decoding process have demonstrated outstanding error correcting performance with simpler computational process. Furthermore, due to their suitability for parallelization and low complexity hardware implementation, LDPC codes have become a promising alternative to all the other coding schemes in Error Control Coding. Recently, many research works have been accomplished on LDPC decoders and their VLSI implementations to meet the high throughput (over Gb/s) target for advanced high-speed communication systems. However, an efficient design of high throughput LDPC decoder with small size and less power dissipation still remains a great challenge. Therefore, the scope of this thesis is to propose efficient solutions to various issues of the most important practical challenges varying from algorithm techniques to the ASIC / FPGA implementation of LDPC decoders.

#### 3.2 Sum-Product Algorithm with PRDBP

The conventional Sum-Product algorithm (SPA) is integrated with deep belief propagation network proposed PRDBP in iterative message passing method for the precision LLR messages for the input decoding process. The proposed PRDBP model uses the SPA scheme for the decoding process comprises of the two phases for the data transmission between the node edges and tanner graph in the node variables. With the decision-based messaging process the SPA utilizes the information update between the nodes.

Let message transmission is stated as **9**mm for the bit node variables to check node VTC and the message transmission to evaluate the user and variable node is denoted as **9**mm. The conventional SPA model classifies the sign and magnitude with consideration of equation (11)

$$q_{nm} = \mu_{nm} \cdot \lambda_{nm} =$$

sign(q<sub>nm</sub>) and  $\lambda_{nm} = |q_{nm}|$

(11) With the decoding process for the iteration

count of 0 for the messages  $q_{nm}^{(0)} = \frac{2y_i}{\sigma^2}$ with consideration of logarithmic-likelihood ratio information (LLR). The input of the receiver is stated as  $\mathcal{Y}_{\mathbf{i}}$  and variance is represented as  $\sigma$  with consideration of Additive White Gaussian Noise channel. (AWGN) The channel intrinsic information in the channel computes the node variables to perform decoding process presented based on check node unit (CNU) for the information update computed as in equation (12)

$$r_{\min} = 2\{\prod_{i \in \mathcal{N}(m) \mid n} \operatorname{sign}(y_i)\} \cdot \tanh^{-1}\{\prod_{i \in \mathcal{N}(m) \mid n} \tanh\left(\frac{2|y_i|}{x}\right)$$

(12)

(15)

Where in above equation (12) the number

of bits for the mth check is represented as N(m). The message updated and transmitted is denoted as

**F**min utilized for the effective processing and the updated VTC information are presented in equation (13)

$$q_{nm} = q_{mn}^{(0)} + \sum_{m \in \mathcal{M}(n) \setminus m', m' \neq m} r_{min} \quad (13)$$

where M(n) represents the nth bit participating check count using equation (14)

$$q_{n} = q_{nm}^{(0)} + \sum_{m \in M(n)} r_{mn}$$

(14)

The process of decoding is computed based on the parity check for the computation of codewords or maximal iteration count. The implementation of LDPC code is evaluated with the soft decision process for the decoding and SPA provides the higher BER rate. However, the computational complexity is higher for the SPA is not effective for the hardware implementation. The proposed PRDBP model comprises of multiplication and division process to check node with the soft information computation. The performance of proposed PRDBP model is compared with SPA model for the reduction of computational complexity with the reduced quantization values. The proposed PRDBP model uses the hyperbolic tangent (tanh) function and its inverse (tanh-1). The inverse hyperbolic tangent (tanh-1) function is presented as in equation (15) and (16)

$$tanh_{modified}(x) = \{tanh(x), if |x| < x_0; sign(x)tanh(x_0), if |x| \ge x_0\}$$

$$tanh_{modified}^{(-1)}(x) = \{tanh^{(-1)}(x), if ||x|| < x_0; sign(x)tanh^{(-1)}(x_0), if ||x|| \ge x_0\}$$

(16)

However, the PRDBP model subjected to drastic reduction of Bit Error Rate (BER) degradation performance value of 0.25dB. The performance is estimated based on application of quantization scheme with the reduction of approximation errors. Additionally, the proposed PRDBP mode approximate the error for the total iteration decoding for the error correction in channel those leads to minimal signal-to-noise ratio.

Decoding with PRDBP based on SPA

| <u>30<sup>th</sup></u> | N | oven | ıber  | 202 | 23. | Vo  | 01.10 | )1. | No  | 22 |

|------------------------|---|------|-------|-----|-----|-----|-------|-----|-----|----|

|                        | C | 2023 | 3 Lit | tle | Lic | n S | Scie  | nti | fic |    |

| ISSN: 1992-8645 |         | www.jatit.org | E-ISSN: 1817-3195 |

|-----------------|---------|---------------|-------------------|

| T1              | 1 00000 |               | (' 1 C' 'I I      |

proposed PRDBP model The computational complexity is minimal compared with the conventional techniques with the average decoding process with conventional methods. The developed PRDBP model uses the logarithmic likelihood-ratio (LLR) consideration of quantization level for the effective decoding process. The proposed PRDBP model incorporates FFT and SPA algorithm with the lattice estimation to achieve the effective decoding performance to minimize the computational complexity in the lattice subgroup elements. However, for the large set of input sequences the process of transmission comprises of the small non-zero elements for the consideration of different channel to achieve higher bandwidth compared with conventional FFT method those are unsuitable. The proposed PRDBP uses the sparseness for the LDPC codes for the higher execution time and resource memory are processed temporarily in data processing. As a result, the suggested PRDBP model's decoding suffers performance from reducing the computational complexity by modifying the check and variable nodes. The proposed PRDBP model reduces the computational complexity by integrating the Fast Fourier Transform with a time shift model. Variable node computations using optimized integer constants speed up the decoding procedure. The variable and check node in the proposed PRDBP model are presented as follows:

Initialization: Initialize the iteration set count of k = 0 to achieve the maximal decoding iteration process set as kmax. For  $0 \le 1 \le 1 - N$ ,  $q_{nm}^{(0)}$  the priority probability is estimated based on bit n. The set is computed using the equation

$$q_{nm}^{(0)} = \frac{2y_i}{\sigma^2}$$

Step 1: Compute the user update range of for  $0 \le m \le M - 1$  and  $0 \le n \le N - 1$ , for the message transmission between variable data transmission

$$\begin{aligned} r_{mn}^{(k)} &= \left[ r_{mn}^{(k)}(0), r_{mn}^{(k)}(1), \dots, r_{mn}^{(k)}(u-1) \right]^{-1} \\ &\text{is computed as in equation (17)} \\ r_{mn}^{(k)} &= \\ &\prod_{i \in N(m) \setminus n} sign(y_i).F^{-1}\left( \prod_{i \in N(m) \setminus n} F\left(\frac{2|y_i|}{\sigma^2}\right) \right) \end{aligned}$$

Where in above equation (17) F and F represents the discrete Fourier transform and its

| v.jani.org             | E-155IV. 1017-5175           |

|------------------------|------------------------------|

|                        | form respectively. Similarly |

| alphabet size is compu | ted as in equation (18)      |

| $r_{mn}^{(k)} =$       |                              |

| 2020                   |                              |

$$\prod_{i \in N(m) \setminus n} sign(y_i).FFT_h^{-1}\left(\prod_{i \in N(m) \setminus n} FFT_h\left(\frac{2|y_i|}{\sigma^2}\right)\right)$$

(18)

where  $FFT_{h}$  and  $FFT_{h}^{-1}$  represents the FFT based on time shift and inverse process in the 5G communication.

Step 2: Update the variable for

$$0 \le m \le M - 1$$

and  $0 \le n \le N - 1_{\text{the}}$

message  $q_{nm}$  is computed as in equation in (19)  $q_{mn}^{(k)} =$

$$\sum_{m \in \mathcal{M}(n)} \left( \prod_{i \in \mathcal{N}(m) \setminus n} sign(y_i) \cdot FFT_h^{-1} \left( \prod_{i \in \mathcal{N}(m) \setminus n} FFT_h \left( \frac{2|y_i|}{\sigma^2} \right) \right) \right)$$

(19)

$$q_{nm} + q_{nm}^{(0)} + \sum X_i$$

as

presented in equation (20)  $q_{n}^{(k)} = q_{nm} + \sum_{m \in \mathcal{M}(n)} \left(1 - 2\left(S_{m} \oplus z_{n}^{(k)}\right)\right) \left(FFT_{h}^{-1}\left(\sum_{i \in \mathcal{N}(m)} FFT_{h}\left(\frac{2|y_{i}|}{\sigma^{2}}\right)\right)\right)$

Where.

(20)

Step 3: Decision: The hard decision  $Z^{(0)} = \left(Z_0^{(0)}, Z_1^{(0)}, \dots, Z_{N-1}^{(0)}\right)_{\text{is made such}}$ that  $z_n^{(k)} = 0$  if,  $q_n^{(k)} \ge 0$  and  $z_n = 1$  if,  $q_n^{(k)} < 0$ . If  $z_n^{(k)} \cdot H_{mn}^T = 0$ , Output  $Z^{(k)}$  as the decoded codeword and the decoding process is stopped, else the decoding process is started again from Step 1.

Step 4: The process is continued until the maximal decoding iteration to achieve the parity check condition satisfaction for the codeword estimation computed as  $\hat{c} \cdot H^T = 0$ .

The proposed PRDBP model perform the process of node update with the consideration of complex hyperbolic tangent function. The created model computes the process of updating nodes using the Fast Fourier Transform in the presence of a time shift function. When transmitting information, any difference between the Fast Fourier Transform and an FFT-based tangent function is interpreted as a data shift. The implementation of FFT increased the throughput with the reduced computation time for the large information data sets. Additionally, the proposed model does not require any additional memory for the resource leads to reduced area for the temporary data for each iteration. The implementation of FFT function achieves the throughput value of 0.1dB compensated with the implementation of integer optimization for the

<u>30<sup>th</sup> November 2023. Vol.101. No 22</u> © 2023 Little Lion Scientific

#### ISSN: 1992-8645

www.jatit.org

E-ISSN: 1817-3195

process variable update. The integer constant is optimized with the heuristic simulation for the improved performance in decoding process. Furthermore, the proposed PRDBP model decoding process minimizes the LLR values for the initial decoding process. The original values are updated for every decoding step utilized for each decoding process [29].

#### 4. RESULTS AND DISCUSSIONS

The implemented using PRDBP algorithm for error correction simulated using Xilinx 12.4 ISE tool and using Verilog language. Figure below show the simulation result of the PRD G-LDPC encoder, representing the encoder waveform without error. Below simulated encoder output doesn't have any wrong in binary values. Final yield is same as input with all syndromes Zeros.

Figure 2: Simulation Encoding Process

Below simulated encoder output has multiple wrong binary values. Final yield is same as input with all syndromes non zeros.

Below report represents Logical requirements for constructing proposed LDPC for calibrations of LUT and flipflops along with whole area result. From this figure we can say that for this design we use 6272 lookup tables and 2048 flipflops and the area of the whole circuit covered is 0.04383mm2.

# Figure 4: Device utilization summery

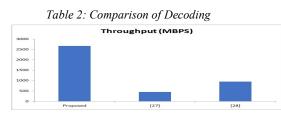

Below snapshot is used to calculate total through put of the proposed system. From the below figure we can say that the total throughput of the system design is 2663MBPS and which is better than the previous works which are discussed in the literature and the results are compared in the table

Figure 5: Timing Summery

| Decoding           |          | Decoding |        |             |        |         |  |  |  |  |

|--------------------|----------|----------|--------|-------------|--------|---------|--|--|--|--|

|                    |          | WLA      | N      |             | Wi-MAX |         |  |  |  |  |

|                    | (648,32  | 4)       | (1296, | (1296, 864) |        | 4,1152) |  |  |  |  |

|                    | SNR (dB) | Bit      | SNR    | Bit         | SNR    | Bit     |  |  |  |  |

|                    |          | Error    | (dB)   | Error       | (dB)   | Error   |  |  |  |  |

|                    |          | Rate     |        | Rate        |        | Rate    |  |  |  |  |

| SPA                | 2.38     | 10-4     | 2.47   | 10-5        | 2.08   | 10-5    |  |  |  |  |

| FFT SPA            | 2.44     | 10-4     | 2.58   | 10-5        | 2.18   | 10-5    |  |  |  |  |

| SSPA               | 2.49     | 10-4     | 2.79   | 10-5        | 2.37   | 10-5    |  |  |  |  |

| MSPA               | 2.59     | 10-4     | 2.97   | 10-5        | 2.39   | 10-5    |  |  |  |  |

| Proposed algorithm | 2.40     | 10-4     | 2.51   | 10-5        | 2.12   | 10-5    |  |  |  |  |

| aigoritiiii        |          |          |        |             |        |         |  |  |  |  |

Table 1: Comparison of Throughput

<u>30<sup>th</sup> November 2023. Vol.101. No 22</u> © 2023 Little Lion Scientific

#### Figure 6: Comparison of Performance

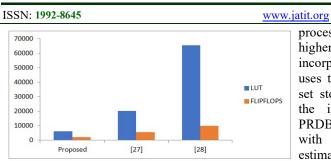

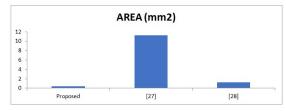

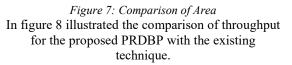

The figure 6 provides the comparison of the LUT and Flipflops for the proposed with the conventional methods. The complexity of the proposed model is minimal compared with the existing techniques. In figure 7 the ara utilization ofr the proposed PRDBP area compared with the existing techniques. The area required for the proposed PRDBP exhibits the minimal requirement in area.

Figure 8: Comparison of Throughput

The comparison of throughput illustrated that proposed PRDBP model achieves the higher throughput compared with the existing techniques. The decoding process performance for the different standards are presented in table 2.

The comparative analysis of proposed PRDBP is examined with other methods such as FFT SPA, SSPA and MSPA as presented in table 2. The comparative analysis expressed that proposed PRDBP achieves the effective performance for decoding compared with the FFT SPA, MSPA and SSPA. The decoding algorithm incorporates arithmetic operation for the determination of node

E-ISSN: 1817-3195 process and conventional SPA model subjected to complexity higher computational with the incorporation of FFT. Furthermore, the SPA model uses the look-up-tables (LUTs) for the large data set storage processing information acquired from the iterative message process. The proposed PRDBP model with the FFT function implemented with time shift adopts the non-linear function estimation with the quantization table approximation. The proposed PRDBP model computational complexity is presented with conventional methods are presented in table 3.

Table 3: Comparison of Computational Complexity

| Alphabet<br>Size u | Sum<br>Product<br>Algorithm | FFT based Sum<br>Product<br>Algorithm | PRDBP |  |

|--------------------|-----------------------------|---------------------------------------|-------|--|

| 2                  | 144                         | 96                                    | 84    |  |

| 4                  | 480                         | 288                                   | 216   |  |

| 8                  | 1728                        | 864                                   | 378   |  |

In table 3 it is observed that proposed PRDBP model is comparatively examined with the SPA model with consideration of arithmetic operation for the decoding and validation process. Through comparative analysis it is observed that proposed PRDBP achieves the reduced arithmetic operation range of 67% and 42% reduction for the total decoding process of arithmetic operations compared with SPA and FFT respectively. Furthermore, the table 3 LPDC model alphabet size increases the complexity for the computation is increased gradually but minimal than the existing techniques. It is also seen that the suggested PRDBP model outperforms the standard SSPA, FET SPA and MSPA in decoding the LDPC codes

|                  | LUT   | FLIPFLOPS | AREA (mm2) | Throughput<br>(MBPS) |

|------------------|-------|-----------|------------|----------------------|

| Proposed         | 6272  | 2048      | 0.04383    | 2663                 |

| [21]             | 20340 | 5593      | 11.25      | 450                  |

| [22]             | 65536 | 10133     | 1.271      | 947                  |

| < 10 <b>00</b> 1 | (     | 4 4 5 6   | 1 (1005 0  | 5.43                 |

(648, 324), (2304, 1152), and (1296, 864), respectively. However, the process of decoding is irregular for the LDPC code to achieve the higher intrinsic message generation for the uniform distribution degree. The proposed PRDBP model normalize the decoding values with the LDPC codes.

Table 4: Comparison of LDPC type

| LDPC           | Code<br>length | Code<br>rate | Nor   | roposed<br>malization<br>⁄alue θ |

|----------------|----------------|--------------|-------|----------------------------------|

|                |                |              | θ1    | θ2                               |

| Irregular Code | 1944           | 1/2          | 0.825 | 0.846                            |

| Irregular Code | 1944           | 2/3          | 0.82  | 0.858                            |

| Irregular Code | 1944           | 3/4          | 0.77  | 0.848                            |

30<sup>th</sup> November 2023. Vol.101. No 22 © 2023 Little Lion Scientific

| ISSN: 1992-8645                         |      |     |      |        | z.jatit.org E-ISSN: 1817-3195                           |

|-----------------------------------------|------|-----|------|--------|---------------------------------------------------------|

| Irregular Code                          | 1944 | 5/6 | 0.78 | 0.8275 | length of 1944. The normalized length of code is        |

| Table 4 presented a normalization value |      |     |      |        | represented as 1944 with the code rate of $1/2$ , $2/3$ |

Table 4 presented a normalization value for varying code rate with irregular LDPC code

and 3/4 in simulation.

Table 5: Comparison of Performance

| Parameters            | Proposed work    | [20]            | [21]           | [22]           | [23]       |

|-----------------------|------------------|-----------------|----------------|----------------|------------|

| Code length           | 1944             | 648,1296, 1944  | 648,1296, 1944 | 648            | 1944       |

| Code rate             | 1/2-5/6          | 1/2-5/6         | 1/2 -5/6       | 1/2-5/6        | 1/2        |

| Sub-matrix size       | 81               | 27,54,81        | 27, 54 ,81     | 27             | 81         |

| # of iterations       | 10               | 2-15            | 5              | 11-13          | 8          |

| Clock Frequency (MHz) | 587              | 412             | 500            | 240            | 111.1      |

| Throughput            | 1.27–2.17 (Gb/s) | 61.3–736 (Mb/s) | 1.6 (Gb/s)     | 175-410 (Mb/s) | 250 (Mb/s) |

| Core Area (mm2)       | 1.42             | 3.69            | 1.85           | 0.74           | 3.88       |

| Power (mW)            | 140.42           | 502             | 238.4          | 234.6          | 76         |

| TAR (Gbps/mm2)        | 1.456            | 0.199           | 0.865          | 0.554          | 0.0644     |

In table 5 proposed PRDBP model achieves the higher throughput for the efficient utilization of resources with reduced area compared with the other decoders. The proposed PRDBP model is reconfigured based on the block length and code rate for the IEEE 802.11n standard.

Table 6 presented a comparative analysis of the proposed PRDBP with the existing algorithm, . The comparative analysis stated that proposed PRDBP model exhibits the faster convergence with the increased throughput with reduced area.

| No. of<br>Iterations |                 |               | Mackay'sLDPC (2000, 1000) |                 |                  | FG LDPC (4095, 3367) |                 |               |                 |

|----------------------|-----------------|---------------|---------------------------|-----------------|------------------|----------------------|-----------------|---------------|-----------------|

|                      | IERRWBF<br>(ms) | Proposed (ms) | Speed Up<br>(%)           | IERRWBF<br>(ms) | Proposed<br>(ms) | Speed<br>Up (%)      | IERRWBF<br>(ms) | Proposed (ms) | Speed Up<br>(%) |

| 5                    | 7.82            | 5.49          | 42.44                     | 15.40           | 10.22            | 50.68                | 58.41           | 37.79         | 54.56           |

| 10                   | 14.37           | 9.81          | 46.84                     | 29.97           | 19.51            | 53.61                | 284.26          | 177.33        | 60.30           |

| 25                   | 41.23           | 27.53         | 49.76                     | 138.21          | 87.88            | 57.27                | 561.39          | 345.91        | 62.29           |

| 50                   | 74.28           | 49.32         | 50.61                     | 269.85          | 168.19           | 60.44                | 836.15          | 510.68        | 63.73           |

| 75                   | 115.46          | 72.94         | 58.29                     | 396.61          | 245.72           | 61.41                | 1119.57         | 682.12        | 64.13           |

| 100                  | 147.17          | 91.33         | 61.14                     | 529.48          | 325.33           | 62.75                | 1388.76         | 843.84        | 64.58           |

In addition, the convergence rates for the (1008, 504) PEG, (2000, 1000), and (4095, 3367) FG LDPC codes are 61.14, 62.75, and 64.58%, respectively, when using the proposed PRDBP. It is found that code length is increased with the convergence process of decoding for the effective mitigation in decoding performance. Therefore, the simulation results show that the suggested model accomplishes the better throughput with the reduced area required for the 5G communication while simultaneously lowering the computational complexity.

# 5. CONCLUSION

PRDBP model uses the The proposed FFT model for the effective performance of the LDPC codes. The PRDBP model comprises of the enumerator and reconfigurable codes for the effective communication. The proposed PRDBP model uses the FFT based Deep Belief model for the increased throughput. Simulation analysis expressed that proposed PRDBP model achieves the higher throughput with the reduced area for the wireless communication. The design comprises of the LDPC model uses the FFT model for the integrated with SPA for the reduced area effective in wireless communication. The comparative analysis stated that proposed PRDBP ~34 reduced the area and ~48% increase in the throughput. Need to focus more on latency for future research.

# REFERENCES

- [1] K.Arora, J.Singh, Y.Sandhawa, "A survey on channel coding techniques for 5G wireless networks," Telecommunication Systems, Vol.73, No.4, 2020, pp.637-663.

- H.Cui, F.Ghaffari, K.Le, D.Declercq, J.Lin, [2] Z.Wang, "Design of high-performance and area-efficient decoder for 5G LDPC codes", IEEE Transactions on Circuits and Systems I: Regular Papers, Vol.68, No.2, 2020, pp.879-891.

- A.Ly, Y.Yao, "A review of deep learning in [3] 5G research: Channel coding, massive MIMO, multiple access, resource allocation, and network security", IEEE Open Journal of the Communications Society, Vol.2, 2021, pp.396-408.

- [4] B.Wang, Y.Zhu, J.Kang, "Two effective scheduling schemes for layered belief propagation of 5G LDPC codes", IEEE

2 oth NT 1 2022 37 1 101

Check

Information

pp.627-640.

LDPC

NR

arXiv:2212.10245, 2022. [13] S.Habib, A.Beemer, J.Kliewer,

Matrices", *arXiv*

propagation decoding of short graph-based

channel codes via reinforcement learning",

Theory, Vol.2,

Propagation Decoding of CRC Concatenated

Polar

[14] M.Zhu, M.Jiang, C.Zhao, "Adaptive Belief

and

IEEE Journal on Selected Areas in

|      | 30 <sup>th</sup> November 2023. Vol.101. No 22<br>© 2023 Little Lion Scientific                                                                                                                                                                          |                                                                                                                                                                                                        |                                                                                                  |  |  |  |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|--|--|--|

| ISSN | J: 1992-8645 www                                                                                                                                                                                                                                         | .jatit.org                                                                                                                                                                                             | E-ISSN: 1817-3195                                                                                |  |  |  |

|      | <i>Communications Letters</i> , Vol.24, No.8, 2020, pp. 1683-1686.                                                                                                                                                                                       |                                                                                                                                                                                                        | unications, Vol.70,                                                                              |  |  |  |

| [5]  | V.L.Petrović, D.M.El Mezeni, A.Radošević,<br>"Flexible 5G new radio LDPC encoder<br>optimized for high hardware usage<br>efficiency", <i>Electronics</i> , Vol.10, No.9, 2021,<br>pp. 1106.                                                              | [15] K.Y.Kuo, C.Y.Lai, "Refined<br>decoding of sparse-g<br>codes", <i>IEEE Journal on S</i><br><i>Information Theory</i> , Vol.1<br>pp.487-498.                                                        | graph quantum<br>Selected Areas in                                                               |  |  |  |

| [6]  | M.Stark, L.Wang, G.Bauch, R.D.Wesel,<br>"Decoding rate-compatible 5G-LDPC codes<br>with coarse quantization using the information<br>bottleneck method," <i>IEEE Open Journal of the</i><br><i>Communications Society</i> , Vol.1, 2020, pp.646-<br>660. | [16] X.Zhang, M.Jiang, M.Zhu,<br>"CRC-Aided Adaptive Bo<br>Decoding of NR LDPC Cod<br>95th Vehicular<br>Conference:(VTC2022-Sprin<br>1-6, IEEE.                                                        | elief Propagation<br>es", In 2022 IEEE<br>Technology                                             |  |  |  |

| [7]  | J.Boiko, I.Pyatin, O.Eromenko, "Determining<br>the Effectiveness of LDPC Codes for 5G<br>Information Networks", In 2021 IEEE 12th<br>International Conference on Electronics and<br>Information Technologies (ELIT)2021, (pp.<br>159-164). IEEE.         | [17] W.Lin, Z.Xu, S.Hong, L.Wa<br>Joint Belief Propagation<br>Perturbation for JSCC Syste<br>LDPC Codes," In 202<br>Conference on Computer,<br>Telecommunication Systems                               | Decoding with<br>em Based on DP-<br><i>l International</i><br><i>Information and</i>             |  |  |  |

| [8]  | J.Nadal, A.Baghdadi, "Parallel and flexible 5G<br>LDPC decoder architecture targeting FPGA",<br><i>IEEE Transactions on Very Large Scale</i><br><i>Integration (VLSI) Systems</i> , Vol.29, No.6,<br>2021, pp.1141-1151.                                 | <ul> <li>1-5). IEEE.</li> <li>[18] K.Y.Kuo, C.Y.Lai, "Exploit<br/>belief propagation decodi<br/>codes," <i>npj Quantum Informa</i><br/>2022, pp.1-9.</li> </ul>                                        | ng of quantum                                                                                    |  |  |  |

| [9]  | H.Lee, Y.S.Kil, M.Jang, S.H.Kim, O.Sark, G.<br>Park, "Multi-round belief propagation<br>decoding with impulsive perturbation for short<br>LDPC codes", <i>IEEE Wireless Communications</i><br><i>Letters</i> , Vol.9, No.9, 2020,pp. 1491-1494.          | Workshops (GC Wkshps, 20)<br>1-6. IEEE.                                                                                                                                                                | des with scalar<br>EEE Globecom<br>20, December, pp.                                             |  |  |  |

|      | T. C. Y.Chang, P. H.Wang, J. J.Weng, I. H.Lee, Y. T. Su, "Belief-propagation decoding of LDPC codes with variable node-centric dynamic schedules", <i>IEEE Transactions on Communications</i> , Vol.69, No.8, 2021, pp.5014-5027.                        | rate for model selection<br>compression using belief propa<br><i>Annals of Telecommunication</i><br>2020, pp. 623-633.<br>[21] L.Deng, Z.Liu, Y.L.Guan,                                                | in interactive<br>agation decoding,"<br><i>as</i> , Vol.75, No.11,                               |  |  |  |

|      | Z.Yang, Y.Fang, G.Cai, G.Zhang, P.Chen,<br>"Design and optimization of tail-biting<br>spatially coupled protograph LDPC codes<br>under shuffled belief-propagation decoding",<br><i>IEEE Communications Letters</i> , Vol. 24, No.7,<br>2020, 1378-1382. | <ul> <li>X.Yu, Z.Shi, "Perturbed<br/>Propagation Decoding for Hig<br/>Check Codes", <i>IEEE T</i>.<br/><i>Communications</i>, Vol.69, No.4<br/>2079.</li> <li>[22] H.Wang, W.Zhang, Y.Jing,</li> </ul> | Adaptive Belief<br>gh-Density Parity-<br>ransactions on<br>4, 2020, pp. 2065-<br>Y.Chang, Y.Liu, |  |  |  |

| [12] | S.Miao, A.Schnerring, H.Li, L.Schmalen,<br>"Neural Belief Propagation Decoding of<br>Quantum LDPC Codes Using Overcomplete                                                                                                                               | "Controversial Variable Node<br>Adaptive Belief Propage<br>Algorithm Using Bit Flipping                                                                                                                | ation Decoding                                                                                   |  |  |  |

- Systems", *Entropy*, Vol.24, No.3, 2022, pp.427. [23] Sina Pourjabar and Gwan S. Choi, "A High-Throughput Multi-Mode LDPC Decoder for 5G NR" in proceedings of Pourjabar2021AHM, 2021

- [24] Xiumin Wang, Jun Li, Hong Chang, Jinlong He, "Optimization Design of Polar-LDPC Concatenated Scheme on Deep Based Learning," Computers Electrical & Engineering, Volume 84, 2020.

preprint

"Belief

2021,

Codes", IEEE

No.2,

$\frac{30^{\underline{\text{th}}} \text{ November 2023. Vol.101. No 22}}{@ 2023 \text{ Little Lion Scientific}}$

| ISSN: 1992-8645                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | www.jatit.org                                                                                                                                                                   | E-ISSN: 1817-3195 |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|

| <ul> <li>[25] Oscar Ferraz et al., "A Survey<br/>Throughput Non-Binary LDPC<br/>ASIC, FPGA, and GPU Architecture<br/>Communications Surveys &amp; Tutorials<br/>No. 1, First Quarter 2022.</li> <li>[26] Lenin, D. S., and Shekhar, H. (2021<br/>and Implementation of Optimized I<br/>SDR Applications. International Tr<br/>Journal of Engineering, Manage<br/>Applied Sciences &amp; Technologie<br/>12A10,<br/>http://TUENGR.COM/V12/12A10.pd<br/>10.14456/ITJEMAST.2021.15</li> <li>[27] Ahmed Mahdi et al., "A Multirate Ful<br/>LDPC Encoder for the IEEE 802.11n/<br/>LDPC Codes Based on Reduced C</li> </ul> | on High-<br>Decoders:<br>es", IEEE<br>s, Vol. 24,<br>l). Design<br>LDPC for<br>ransaction<br>ment, &<br>rs, 12(1),<br>1-10.<br>lf DOI:<br>ly Parallel<br>ac/ax QC-<br>omplexity | E-ISSN: 1817-3195 |

| <ul> <li>XOR Trees," IEEE Transactions<br/>Large-Scale Integration (VLSI) Syst<br/>29, No. 1, January 2021.</li> <li>[28] Hangxuan Cui et al., "Design<br/>Performance and Area-Efficient Decod<br/>LDPC Codes," IEEE Transactions of<br/>and Systems—I: Regular Papers, 2020</li> <li>[29] P. Girish and B. T, "Intuitive Pro<br/>Conditional Approach in LDPC for<br/>Corrections," 2022 IEEE North<br/>Subsection Flagship International C<br/>(NKCon), Vijaypur, India, 2022, pp.<br/>10.1109/NKCon56289.2022.10126844.</li> </ul>                                                                                 | ems, Vol.<br>of High-<br>der for 5G<br>n Circuits<br>).<br>obabilistic<br>· Memory<br>Karnataka<br>Conference<br>1-7, doi:                                                      |                   |